Mateus Gonçalves Silva

# Digital Design of a Forward Error Correction System for IEEE 802.15.7

Belo Horizonte

2020

Mateus Gonçalves Silva

# Digital Design of a Forward Error Correction System for IEEE 802.15.7

Dissertation submitted to the Graduate Program in Electrical Engineering at Universidade Federal de Minas Gerais, in partial fulfillment of the requirements for the degree of Master in Electrical Engineering.

Supervisor: Prof. Dr. Ricardo de Oliveira Duarte

Belo Horizonte 2020

| S586d | Silva, Mateus Gonçalves.<br>Digital design of a forward error correction system for IEEE 802.15.7<br>[recurso eletrônico] / Mateus Gonçalves Silva. – 2020.<br>1 recurso online (149 f. : il., color.) : pdf.                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Orientador: Ricardo de Oliveira Duarte.                                                                                                                                                                                                        |

|       | Dissertação (mestrado) Universidade Federal de Minas Gerais,<br>Escola de Engenharia.                                                                                                                                                          |

|       | Anexos: f. 127-149.                                                                                                                                                                                                                            |

|       | Bibliografia: f. 121-126.<br>Exigências do sistema: Adobe Acrobat Reader.                                                                                                                                                                      |

|       | <ol> <li>Engenharia elétrica - Teses. 2. Sistemas digitais - Teses.</li> <li>Propriedade intelectual - Teses. I. Duarte, Ricardo de Oliveira. II.</li> <li>Universidade Federal de Minas Gerais. Escola de Engenharia. III. Título.</li> </ol> |

|       | CDU: 621.3(043)                                                                                                                                                                                                                                |

|       |                                                                                                                                                                                                                                                |

Ficha catalográfica: Biblioteca Profº Mário Werneck, Escola de Engenharia da UFMG.

FW UNIVERSIDADE FEDERAL DE MINAS GERAIS Escola de Engenharia Programa de Pós-Graduação em Engenharia Elétrica UNIVERSIDADE FEDERAL DE MINAS GERAIS Mateus Gonçalves Silva Dissertação de Mestrado submetida à Banca Examinadora designada pelo Colegiado do Programa de Pós-Graduação em Engenharia Elétrica da Escola de Engenharia da Universidade Federal de Minas Gerais, como requisito para obtenção do grau de Mestre em Engenharia Elétrica. Aprovada em 15 de dezembro de 2020. Rch Q. H Por: Prof. Dr. Ricardo de Oliveira Duarte - Orientador DELT (UFMG) Truis Willain at With Multers, Prof. Dr. Davies William de Lima Monteiro DEE (UFMG) Prof. Dr. Frank Sill Torres DELT (UFMG) Prof. Dr. Datton Martini Colombo DEE (UFMG)

# Agradecimentos

Esta dissertação de mestrado é um resultado de um processo de formação acadêmica e cidadã fornecido pela Universidade Federal de Minas Gerais (UFMG), iniciado nos tempos de graduação. Por isso sou grato à UFMG pelo suporte dado durante esses anos e aos seus membros que acreditam em um ensino público, de qualidade e inclusivo. Em especial, agradeço ao Prof. Dr. Ricardo de Oliveira Duarte, que me acompanhou durante a maior parte deste processo como professor, orientador e amigo. Também agradeço aos alunos de iniciação científica Elisa Santos Bacelar e Gabriel Ricardo Thomaz de Araújo pelo esforço e dedicação empenhados na pesquisa e pela contribuição fundamental para este trabalho.

Estendo a minha gratidão aos professores do OptMA Lab, principalmente aos Prof. Dr. Davies William de Lima Monteiro, Prof. Dr. Frank Sill Torres, e Prof. Dr. Dalton Martini Colombo que aceitaram compor a banca de avaliação deste trabalho. Agradeço também à Cadence Design Systems pelo suporte dado a mim durante este período de pesquisa.

Agradeço o suporte de todos os meus familiares e amigos próximos. Principalmente, da minha amável companheira Lívia Teixeira Duarte, por seu cuidado e incentivo dispensados a mim durante esta jornada. Dedico esta dissertação a minha mãe (Célia Regina Gonçalves) e ao meu pai (Jairo da Silva), que sempre me ampararam com muito amor e resiliência.

### Acknowledgements

This master thesis is a result of a process for academic and citizen formation carried out by the Universidade Federal de Minas Gerais (UFMG), started at the undergraduate period. For that reason, I am grateful to UFMG for the support provided over these years and to its members who believe in a public, high quality and inclusive education. In particular, I thank the Prof. Dr. Ricardo de Oliveira Duarte, who guided me during most of this process as a teacher, advisor and friend. I also thank the undergraduate students Elisa Santos Bacelar and Gabriel Ricardo Thomaz de Araújo for their effort and dedication committed to the research and for their fundamental contribution to this work.

I extend my gratitude to the professors at OptMA Lab, especially to Prof. Dr. Davies William de Lima Monteiro, Prof. Dr. Frank Sill Torres, and Prof. Dr. Dalton Martini Colombo who agreed to serve on my master's thesis evaluation committee. I also thank Cadence Design Systems for the support provided to me during this research period.

I appreciate the support of all my family and close friends – especially from my lovely partner Lívia Teixeira Duarte, for the affection and encouragement she gave me during this journey. I dedicate this master thesis to my mother (Célia Regina Gonçalves) and my father (Jairo da Silva), who always supported me with love and resilience.

"Cuando uno busca algo, no debe ni soñar en encontrarlo por azar, por lo menos dentro de un plazo determinado. Porque uno de los tantos chistes del azar es, justamente, escondernos lo que buscamos, y hacernos encontrar lo que no buscamos, o que ya no buscamos." (El sótano, Mario Levrero)

### Abstract

Visible Light Communication (VLC) is an emerging field that has attracted attention in recent times, and it has been proposed as a complement or even an alternative to the conventional RF systems. The motivation for it is that the latter is suffering from a phenomenon known as RF spectrum crunch - due to the overuse of wireless communication in user-end applications. The first global attempt to standardize VLC was promoted by IEEE 802.15.7, which specifies the Physical (PHY) and Media Access Control (MAC) layers for short range VLC. It has three PHY layers (I, II, and III) with thirty operating modes suitable for a wide range of noisy channel conditions. The main element of them is the Forward Error Correction (FEC) component, which defines a set of error control techniques Reed Solomon (RS) codes, Interleaving, and Convolutional Codes (CC) employed to improve the capacity of the transmission channel. The goal of this master thesis is to propose a digital system that implements a FEC compliant with IEEE 802.15.7. The main outcome of this work is an open access Intellectual Property (IP) Core for the FEC, followed by a comprehensive explanation of its related Register Transfer Level (RTL) architecture. Most attempts for implementing a IEEE 802.15.7 compliant system is targeted to prototype applications in embedded platforms, whereas dedicated digital devices are more appropriate for the hardware realization of PHY layers. Moreover, the availability of reliable IP Cores for communication such as the FEC and its base blocks is scarce. These facts corroborate the demand for the intended work. Verification and synthesis of the resulting IP Core are carried out by both Field Programmable Gate Array (FPGA) and Application Specific Integrated Circuit (ASIC) flows, and their results for size, timing and power consumption are analyzed and cross validated. IEEE 802.15.7 requirements for throughput and latency are also checked for the FEC IP Core, and they are fulfilled for most operating modes at the target device technologies. Improvements for the digital design architecture and methodology of the FEC IP Core are discussed at the end of this thesis, enabling opportunities for future academic and development projects.

**Keywords**: Digital Systems, Error correction code, IEEE 802.15.7, Intellectual Property, Visible Light Communication

### Resumo

Comunicação por luz visível (VLC Visible Light Communication) é um campo emergente que tem chamado atenção nos últimos tempos, sendo proposto como um complemento ou mesmo uma alternativa aos sistemas de Rádio Frequência (RF) convencionais. A motivação para isso é que estes últimos sofrem de um fenômeno conhecido como RF spectrum crunch devido ao uso exagerado de comunicação sem fio em aplicações de usuário final. A primeira tentativa global de normatizar o VLC foi promovida pelo IEEE 802.15.7, que detalha as camadas física (PHY - Physical) e de Controle de Acesso ao Meio (MAC Media Access Control) para o VLC de alcance curto. O padrão especifica três camadas PHY (I, II, and III) com trinta modos de operação que são adequados para uma ampla gama de cenários de canal ruidoso. O principal elemento dessas camadas é o Forward Error Correction (FEC), que define um conjunto de técnicas de controle de erro códigos Reed-Solomon (RS), Interleaving, Códigos Convolucionais (CC) utilizado para melhorar a capacidade de transmissão do canal. O objetivo desta dissertação de mestrado é propor um sistema digital que implementa um FEC compatível com o IEEE 802.15.7. O principal resultado deste trabalho é uma propriedade intelectual (IP Intellectual Property) de livre acesso para o FEC, acompanhada de uma explicação detalhada da sua arquitetura Register Transfer Level (RTL). Na literatura, a maioria dos esforços para implementar uma camada PHY compatível com o IEEE 802.15.7 é visada para aplicações de prototipação em plataformas embarcadas, enquanto um sistema digital dedicado é mais apropriado para a implementação de camadas PHY. Além do mais, a disponibilidade de IPs confiáveis para a área de comunicação, tais como o FEC e seus blocos básicos, é escassa. Estas constatações corroboram a necessidade de um trabalho como este. A verificação e a síntese do IP resultante é feita tanto no fluxo Field-Programmable Gate Array (FPGA) quanto no Application-Specific Integrated Circuit (ASIC), e os resultados para tamanho, atraso, consumo energético são analisados juntamente com uma validação cruzada dos mesmos. Os requisitos do IEEE 802.15.7 para a taxa de transferência efetiva e a latência também são conferidos para o IP, e eles são satisfeitos para a maioria dos modos de operação, dado os dispositivos selecionados. Melhorias para a arquitetura e a metodologia do projeto digital do FEC IP são discutidas no final desta dissertação, o que habilita oportunidades para futuros projetos acadêmicos e de desenvolvimento.

**Palavras-chave**: Sistemas Digitais, Código de Correção de Erro, IEEE 802.15.7, Propriedade Intelectual, Comunicação por luz Visível

# Contents

|         | List of Figures                                              | 19 |

|---------|--------------------------------------------------------------|----|

|         | List of Tables                                               | 22 |

| 1       | INTRODUCTION                                                 | 31 |

| 1.1     | Visible Light Communication (VLC): Related Terminologies and |    |

|         | Standards                                                    | 32 |

| 1.2     | Forward Error Correction (FEC)                               | 33 |

| 1.3     | Motivation and Goals                                         |    |

| 1.4     | Thesis Roadmap                                               | 35 |

| 2       | IEEE 802.15.7: GUIDED REVIEW                                 | 37 |

| 2.1     | Topologies Types                                             | 39 |

| 2.2     | Architectural Aspects                                        | 40 |

| 2.3     | Physical (PHY) Layer                                         | 40 |

| 2.3.1   | Operation Modes                                              | 42 |

| 2.3.2   | Frame Structure                                              | 44 |

| 2.3.2.1 | Synchronization Header (SHR)                                 | 44 |

| 2.3.2.2 | Physical-layer Header (PHR)                                  | 45 |

| 2.3.2.3 | Header-Check Sequence (HCS)                                  | 45 |

| 2.3.2.4 | Optional Fields                                              | 45 |

| 2.3.2.5 | PHY Service Data Unit (PHY Service Data Unit (PSDU))         | 45 |

| 2.4     | Data Modes                                                   | 45 |

| 2.5     | Dimming and Flicker Mitigation Support                       | 46 |

| 2.6     | PHY Management Service                                       | 46 |

| 2.6.1   | PHY Management Service                                       | 47 |

| 2.6.2   | PHY Data Service                                             | 48 |

| 3       | RELATED WORKS                                                | 49 |

| 3.1     | Prototypes for IEEE 802.15.7 PHY layer                       | 49 |

| 3.1.1   | Gavrincea et al. (2014)                                      | 49 |

| 3.1.2   | Hussain et al. (2015)                                        | 49 |

| 3.1.3   | Turan et al. (2017)                                          | 50 |

| 3.1.4   | Namonta et al. (2017)                                        | 50 |

| 3.1.5   | Hosein et al. (2019)                                         | 51 |

| 3.2     | ASIC Design for IEEE 802.15.7 PHY layer                      | 51 |

| 4       | FORWARD ERROR CORRECTION FOR IEEE 802.15.7                                             | 55   |

|---------|----------------------------------------------------------------------------------------|------|

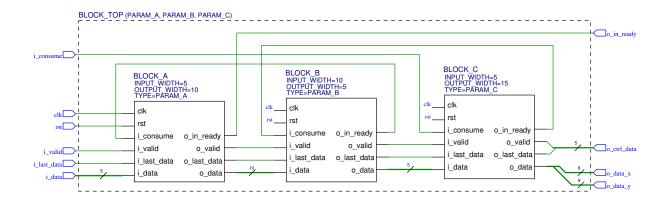

| 4.1     | Generic data protocol interface for Intellectual Property (IP) devel-                  |      |

|         | opment                                                                                 | 55   |

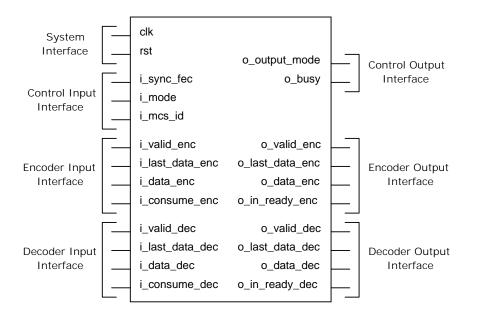

| 4.2     | FEC IP Core Interface                                                                  | 57   |

| 4.3     | Basic building blocks in FEC                                                           | 59   |

| 4.3.1   | Reed-Solomon (RS) Codes                                                                | 59   |

| 4.3.2   | IP Core for RS Codec                                                                   | 63   |

| 4.3.3   | Block Interleaver                                                                      | 63   |

| 4.3.4   | IP Core for Block Interleaver                                                          | 65   |

| 4.3.5   | Convolutional Codes                                                                    | 66   |

| 4.3.5.1 | IP core for Convolutional Encoder                                                      | 68   |

| 4.3.5.2 | IP Core for Viterbi Decoder                                                            | 69   |

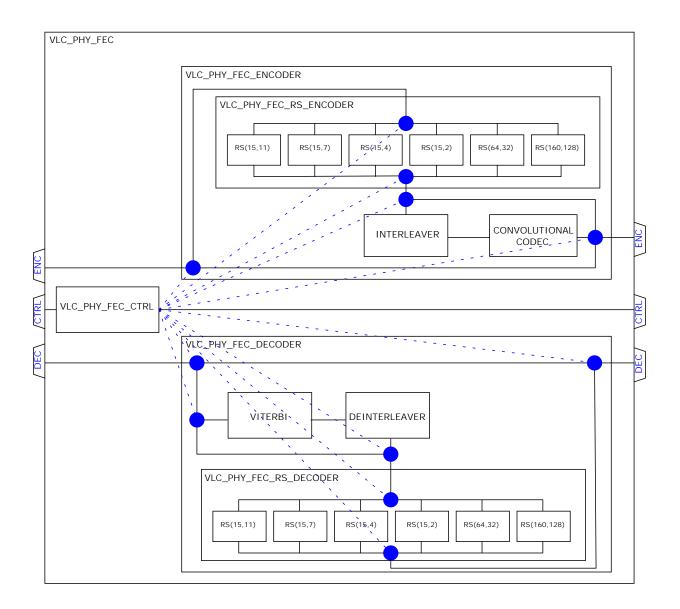

| 4.4     | Top-down architecture view of FEC                                                      | 71   |

| 4.4.1   | FEC Controller                                                                         | 72   |

| 4.4.2   | FEC Encoder                                                                            | 72   |

| 4.4.3   | FEC Decoder                                                                            | 73   |

| 4.4.4   | RS Codec for FEC                                                                       | 73   |

| 4.4.5   | Block Interleaver for FEC                                                              | 75   |

| 4.4.6   | Convolutional Encoder for FEC                                                          | 75   |

| 4.4.7   | Viterbi Decoder for FEC                                                                | 75   |

| 4.4.7.1 | Puncturing and Depuncturing for rates $1/4$ and $2/3$                                  | 75   |

| 4.5     | Summary                                                                                | 77   |

| 5       | RESULTS AND DISCUSSION                                                                 | 79   |

| 5.1     | General Aspects of the FEC IP                                                          |      |

| 5.2     | Verification                                                                           |      |

| 5.2.1   | Connectivity Checking                                                                  |      |

| 5.2.2   | Controller Inspection                                                                  |      |

| 5.2.3   | End-to-End Examination                                                                 |      |

| 5.3     | Synthesis Results                                                                      |      |

| 5.3.1   | Device Technologies                                                                    |      |

| 5.3.1.1 | Altera <sup>®</sup> Cyclone <sup>®</sup> V - 5CGXFC5C6F27C7N                           |      |

| 5.3.1.2 | TCB018GBWP7T stardard cell library from Taiwan Semiconductor Manufacturing             |      |

|         | Company (TSMC) <sup>®</sup> $0.18 \mu m$ Complementary Metal Oxide Semiconductor (CMOS | ) 92 |

| 5.3.2   | Design size                                                                            | ,    |

| 5.3.3   |                                                                                        |      |

| 5.3.4   | Power Consumption                                                                      |      |

| 5.4     | Communication Performance                                                              |      |

| 5.5     | Closing Discussion                                                                     |      |

| 6   | CONCLUSION                                                        |

|-----|-------------------------------------------------------------------|

| 6.1 | Future Works                                                      |

| 6.2 | Final Remarks                                                     |

|     | BIBLIOGRAPHY                                                      |

|     | ANNEX 127                                                         |

|     | ANNEX A – OPERATING MODES IN IEEE 802.15.7 129                    |

|     | ANNEX B – Register Transfer Level (RTL) SCHEMATICS OF FEC         |

|     | IP                                                                |

|     | ANNEX C – STANDARD LIBRARY CELL DETAILS                           |

| C.1 | Cell Types for TCB018GBWP7T                                       |

| C.2 | Glossary of Cell Prefix Code for TCB018GBWP7T                     |

| C.3 | Detailed Report of TCB018GBWP7T Utilization for the FEC IP 139    |

| C.4 | Detailed Report of Generic Standard Cell (GSC) 3.0v Cell Utiliza- |

|     | tion for the FEC IP                                               |

| C.5 | Timing Report of the FEC IP Critical Path using TCB018GBWP7T 145  |

|     | ANNEX D – COMMUNICATION PERFORMANCE DATA OF FEC                   |

|     | IP                                                                |

# List of Figures

| Figure 1 –  | Visible light in electromagnetic spectrum scale ([9], p. 2048)                           | 32 |

|-------------|------------------------------------------------------------------------------------------|----|

| Figure 2 –  | Communication blocks required to transfer data between two end-user                      |    |

|             | devices                                                                                  | 38 |

| Figure 3 –  | Network topologies in IEEE 802.15.7 ( $[13]$ , p. 6)                                     | 39 |

| Figure 4 –  | VPAN device architecture ([13], p.8).                                                    | 41 |

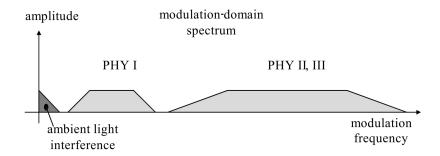

| Figure 5 –  | Frequency spectrum occupied by each PHY layer ([13], p.9)                                | 42 |

| Figure 6 –  | Modulation schemes present in IEEE 802.15.7 PHY layers: OOK (a),                         |    |

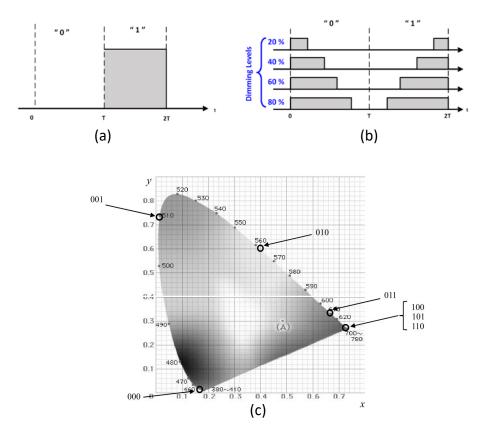

|             | VPPM (b), and CSK (c) ( [24], p. 42 for (a) and (b) [13], p. 254 for (c))                | 43 |

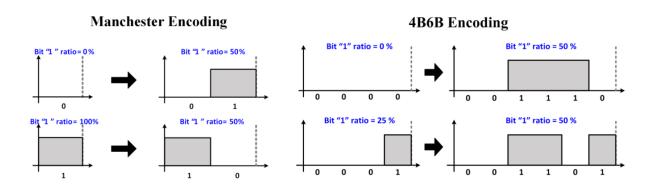

| Figure 7 –  | IEEE 802.15.7 RLL coding conversion examples ([24], p. 41)                               | 43 |

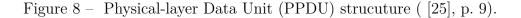

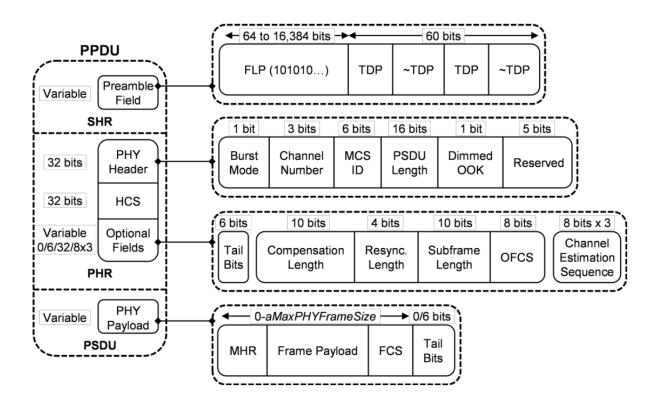

| Figure 8 –  | PPDU strucuture ([25], p. 9)                                                             | 44 |

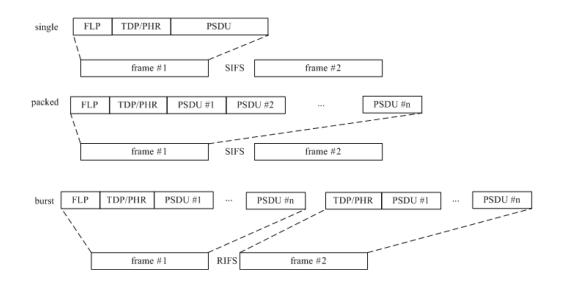

| Figure 9 –  | Data transmission modes in PHY layer ([13], p. 218)                                      | 46 |

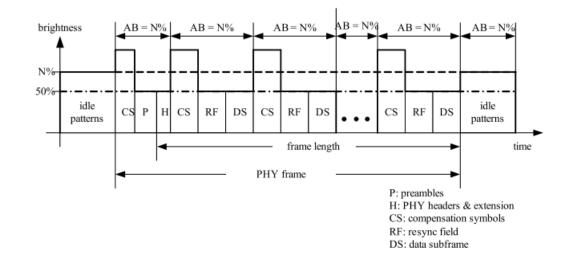

| Figure 10 – | OOK dimming mechanism in IEEE 802.15.7 PHY layer ([13], p. 14).                          | 47 |

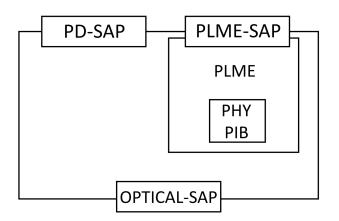

| Figure 11 – | SAP points in PHY layer ( $[13]$ , p. 231)                                               | 47 |

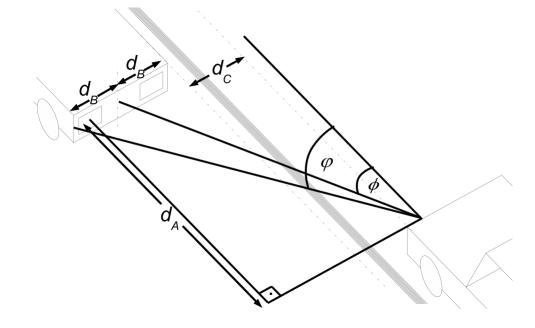

| Figure 12 – | Critical angles $\phi$ and $\varphi$ for vehicle-to-vehicle VLC in opposite directions   |    |

|             | based on the vehicle and lane separation width $(2d_B \text{ and } d_C)$ . These         |    |

|             | angles determine the longitudinal distance between the vehicles for                      |    |

|             | successful communication using visible light ([30], p. 4)                                | 51 |

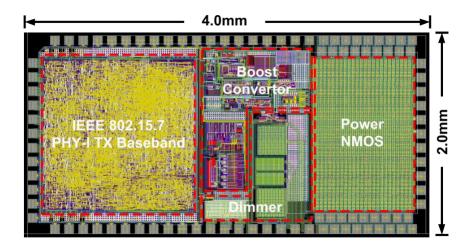

| Figure 13 – | Layout of transmitter SoC ( [25], p. 47)                                                 | 52 |

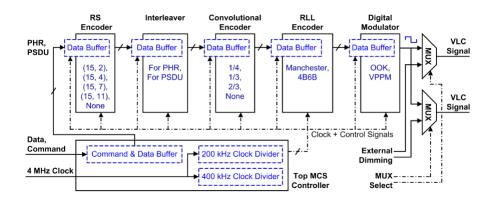

| Figure 14 – | System block diagram of the transmitter ([25], p. 21)                                    | 53 |

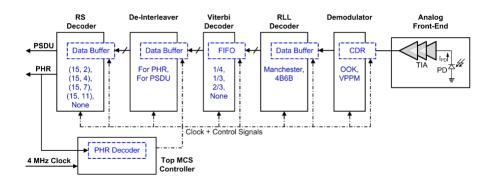

| Figure 15 – | System block diagram of the receiver ([25], p. 48)                                       | 53 |

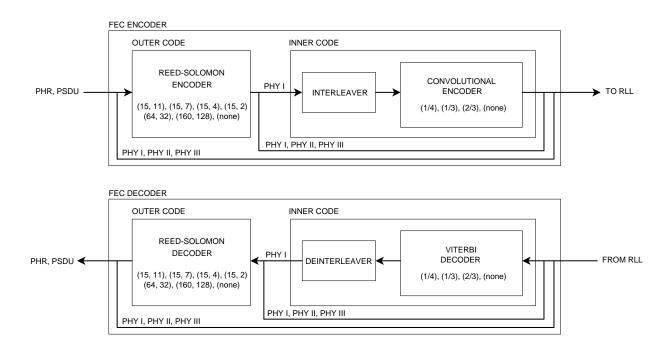

| Figure 16 – | High-level diagram of FEC encoder and decoder for IEEE $802.15.7$                        | 56 |

| Figure 17 – | Generic data protocol interface used in this master thesis                               | 56 |

| Figure 18 – | Block interconnect example using generic data protocol                                   | 57 |

| Figure 19 – | Port interface of VLC_PHY_FEC ports                                                      | 58 |

| Figure 20 – | Description of VLC_PHY_FEC ports                                                         | 59 |

| Figure 21 – | Architectural mapping of MCS ID in FEC IP                                                | 60 |

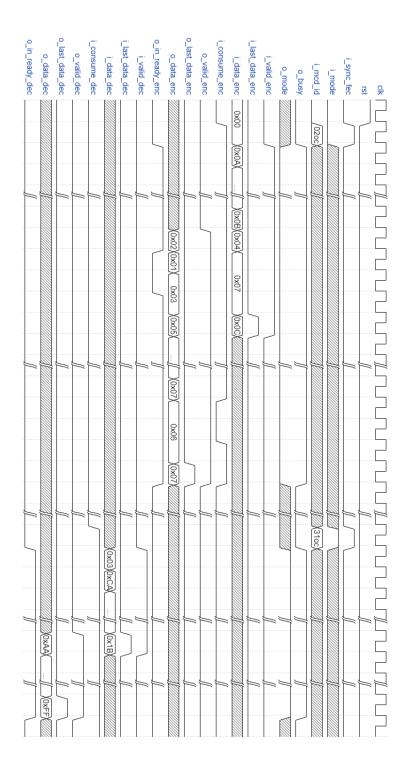

| Figure 22 – | Waveform example for FEC IP utilization                                                  | 61 |

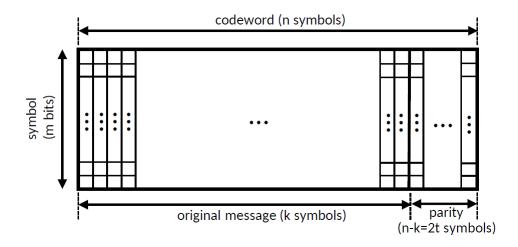

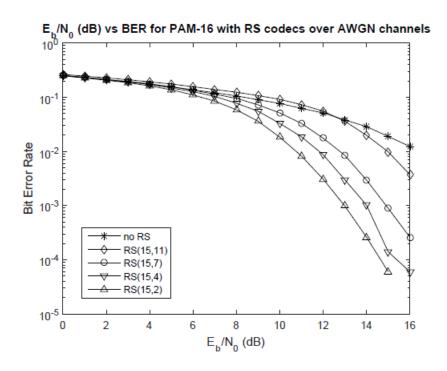

| Figure 23 – | Generic parametric configuration of RS codes ([41], p. 2)                                | 62 |

| Figure 24 – | Transmission efficiency for Pulse-Amplitude Modulation with 16 discrete                  |    |

|             | levels (PAM-16) over Additive White Gaussian Noise (AMGN) channels                       |    |

|             | using RS codecs with n = 15 and k = 11, 7, 4, and 2 with Eb/N0 $$                        |    |

|             | varying from 0 to 16 in a MATLAB $\ensuremath{\mathbb{R}}$ simulation of $10^6$ sampling |    |

|             | transmissions [42]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$       | 62 |

| Figure 25 – | Parameter interface of the RS Codec IP [42]                                              | 63 |

| Figure 26 – | Port interface of the RS Codec IP [42].                                                  | 64 |

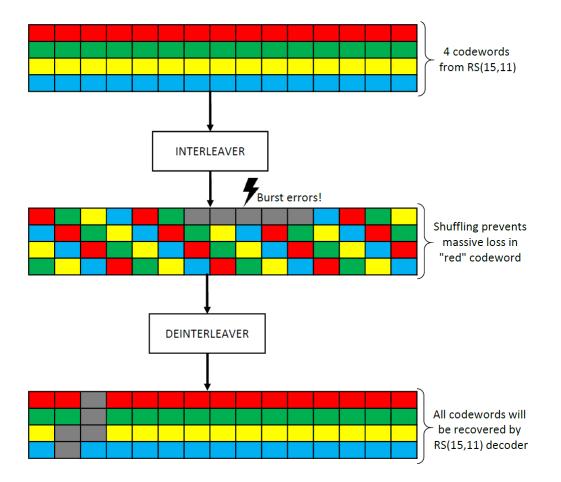

| Figure 27 –  | Interleaver against burst errors. Each color represents a codeword output from RS Encoder                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 28 –  | Parameter interface of the Interleaver [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68 |

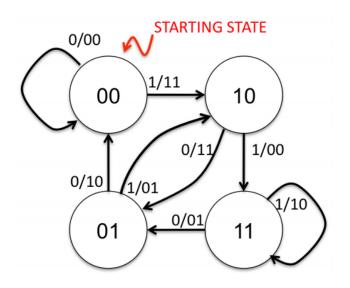

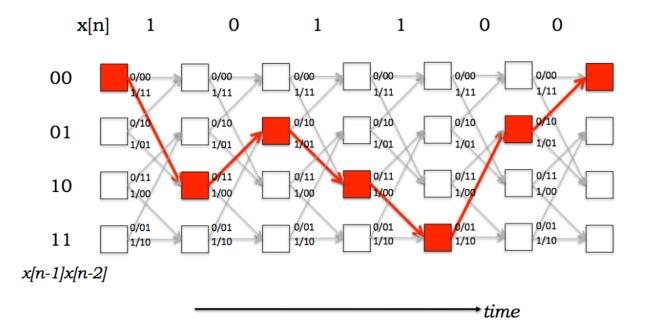

|              | The trellis illustration for the decoding task and the timing unrolling<br>the FSM that represents the number of states hold by the convolutional<br>code $(x[n-1]x[n-2])$ . In red, it is represented the most likely path<br>given the received parity bits, which assemblies the decoded message<br>(x[n]). In each state, the top and the bottom arcs are translated into '0'<br>and '1'. For each state, PM is updated by the BM, and the lowest PM<br>among the states is selected as the decoded sequence at the last time | 69 |

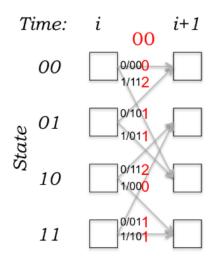

| Figure 33 –  | The BM for hard decision decoding. In this example, the receiver gets<br>the parity bits 00, and each transition receives a score (in red) based on<br>the hamming distance between parity bits represented by the transition<br>and the received bits. The PM of the states in the next iteration $(i + 1)$                                                                                                                                                                                                                      |    |

| <b>T</b>     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70 |

|              | Port interface of the Convolutional Encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71 |

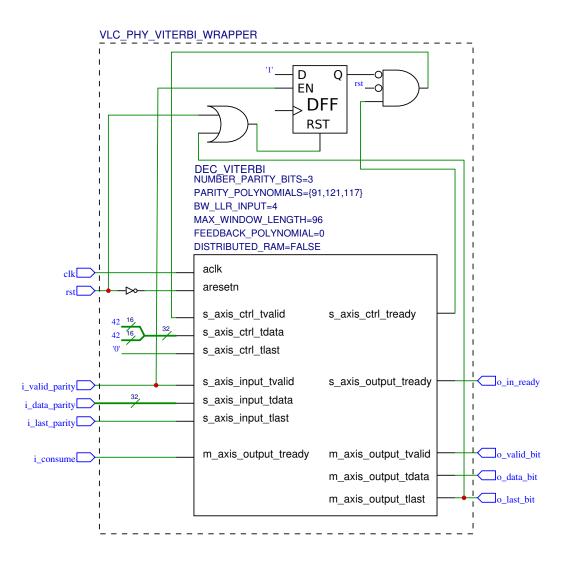

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71 |

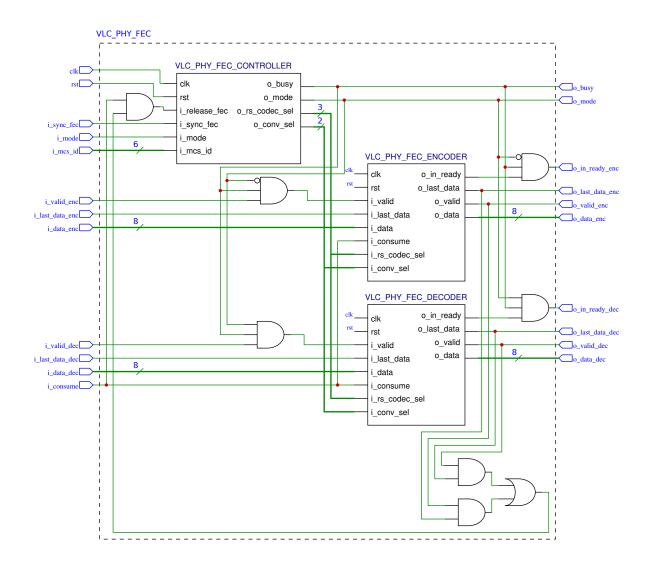

| -            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73 |

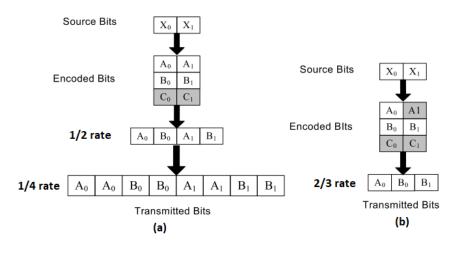

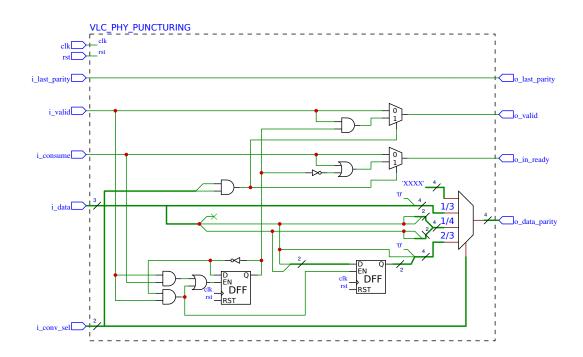

|              | Puncturing of parity bits for rate conversion from 1/3 to 1/4 and 2/3.<br>The 1/4 puncturing (a) removes the third bit of the 1/3 parity output<br>and duplicates the remaining two bits. The 2/3 puncturing (b) performs<br>a interleaved removal of one and two bits of the 1/3 parity output, and                                                                                                                                                                                                                              | 74 |

| D. 41        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76 |

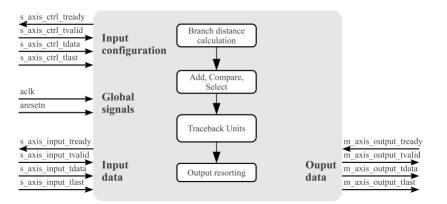

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80 |

| Figure 42 –  | High level diagram of <i>VLC_PHY_FEC</i> with the wire connections<br>between its main sub-blocks. Blue circles represent multiplexing ele-<br>ments controlled by <i>VLC_PHY_FEC_CTRL</i> according to the selected<br><i>MCS_ID</i>                                                                                                                                                                                                                                                                                             | 82 |

| Figure 12    | Checks required for signal connectivity assessment: structural (a), func-                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 04 |

| 1 iguie 40 – |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83 |

| Figure 44 –  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83 |

| Figure 45 – | High level view of the test bench $VLC\_PHY\_FEC\_TB$ responsible                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | for handling the "End-to-End" examination                                                                                                                                               |

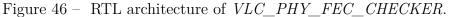

| Figure 46 – | RTL architecture of $VLC\_PHY\_FEC\_CHECKER$                                                                                                                                            |

| Figure 47 – | FSM implemented by $VLC\_PHY\_FEC\_CHECKER\_CTRL$                                                                                                                                       |

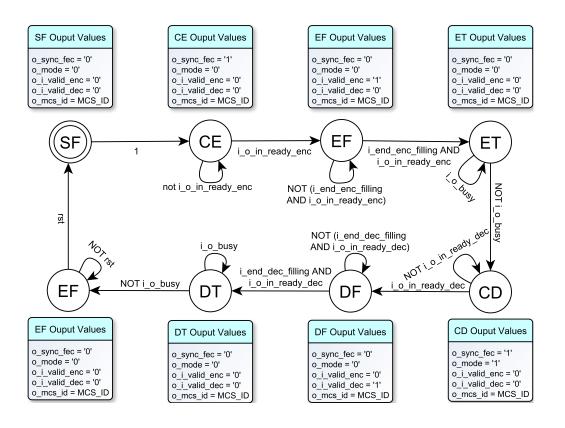

| Figure 48 – | Routine used to assess the $VLC\_PHY\_FEC$ for each MCS ID using                                                                                                                        |

|             | the "End-to-End" test bench                                                                                                                                                             |

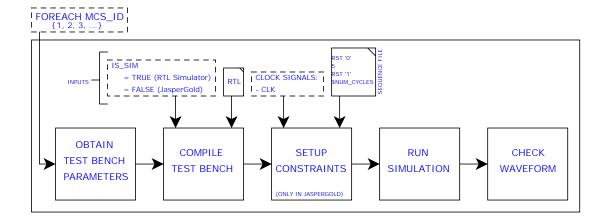

| Figure 49 – | Nomenclature explanation for 5CGXFC5C6F27C7N. (figure adapted                                                                                                                           |

|             | from [56])                                                                                                                                                                              |

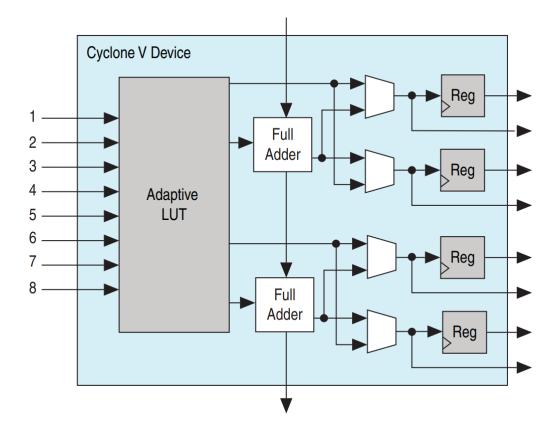

| Figure 50 – | ALM architecture in Cyclone <sup>®</sup> V [55]. Reports for resource usage in                                                                                                          |

|             | FPGA from Quartus <sup>®</sup> Prime are in terms of ALMs. $\dots \dots \dots$          |

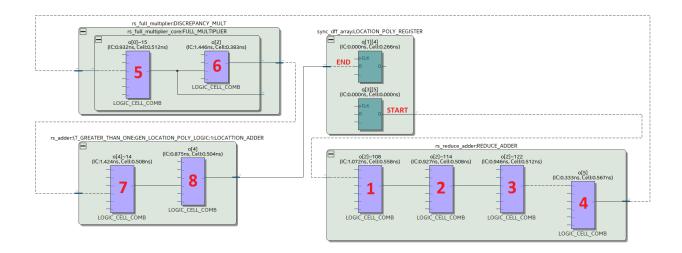

| Figure 51 – | Critical path of the FEC IP for 5CGXFC5C6F27C7N reported by                                                                                                                             |

|             | Quartus <sup>®</sup> Technology Map Viewer. $\dots \dots \dots$                         |

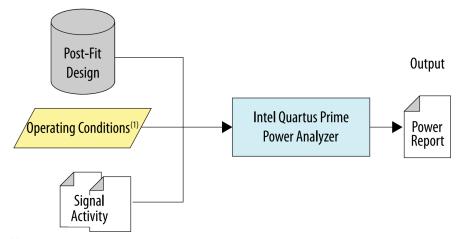

| Figure 52 – | Inputs required for Power Analyzer tool in Quartus $^{\textcircled{B}}$ Prime [63] $~$ 101                                                                                              |

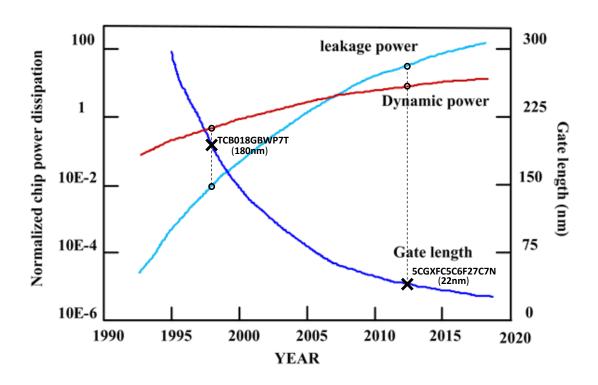

| Figure 53 – | Power dissipation for dynamic and leakage rates according to the tech-                                                                                                                  |

|             | nology node [66] $\ldots \ldots \ldots$                                 |

| Figure 54 – | Timing diagram for the encoder portion of FEC IP $\ldots \ldots \ldots$ |

| Figure 55 – | Timing diagram for the decoder portion of FEC IP $\ldots \ldots \ldots$ |

| Figure 56 – | PHY I operating modes ([13], p. 213)                                                                                                                                                    |

| Figure 57 – | PHY II operating modes ([13], p. 213)                                                                                                                                                   |

| Figure 58 – | PHY III operating modes ( [13], p. 214). $\dots \dots \dots$                            |

| Figure 59 – | Architecture of $VLC\_PHY\_FEC\_CONTROLLER$ described in section                                                                                                                        |

|             | 4.4.1                                                                                                                                                                                   |

| Figure 60 – | Architecture of $VLC\_PHY\_FEC\_ENCODER$ described in section 4.4.2. 132                                                                                                                |

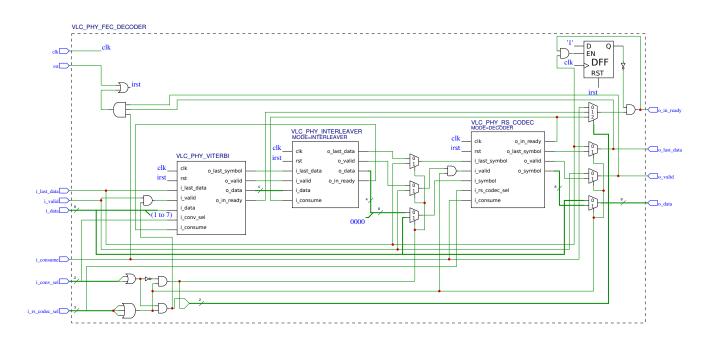

| Figure 61 – | Architecture of $VLC\_PHY\_FEC\_DECODER$ described in section 4.4.3. 132                                                                                                                |

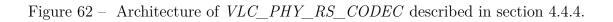

| Figure 62 – | Architecture of $VLC\_PHY\_RS\_CODEC$ described in section 4.4.4 133                                                                                                                    |

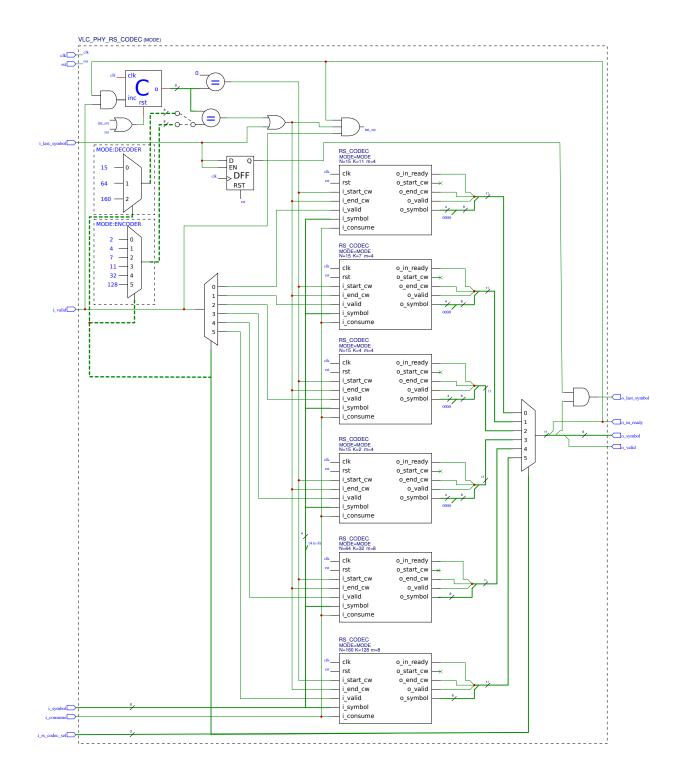

| Figure 63 – | Architecture of $VLC\_PHY\_INTERLEAVER$ described in section 4.4.5. 134                                                                                                                 |

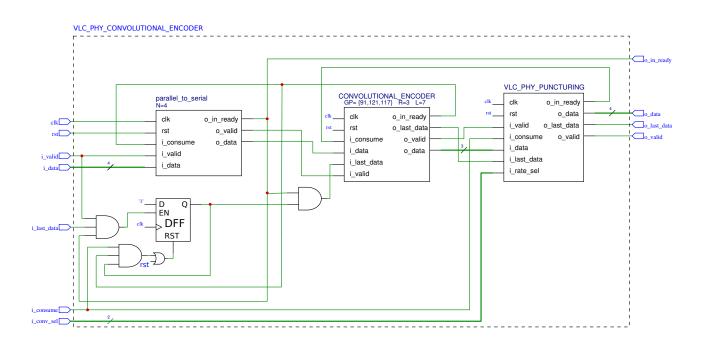

| Figure 64 – | Architecture of $VLC\_PHY\_CONVOLUTIONAL\_ENCODER$ described                                                                                                                            |

|             | in section 4.4.6                                                                                                                                                                        |

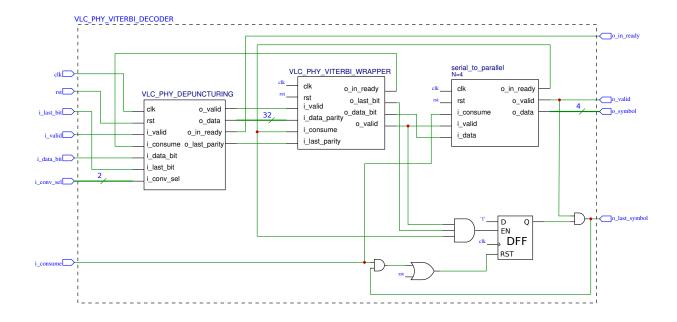

| Figure 65 – | Architecture of $VLC\_PHY\_VITERBI\_DECODER$ described in section                                                                                                                       |

|             | 4.4.7                                                                                                                                                                                   |

| Figure 66 – | Puncturing of parity bits for rate conversion from $1/3$ to $1/4$ and $2/3$                                                                                                             |

|             | described in section $4.4.7.1.$ $\ldots$ $135$                                                                                                                                          |

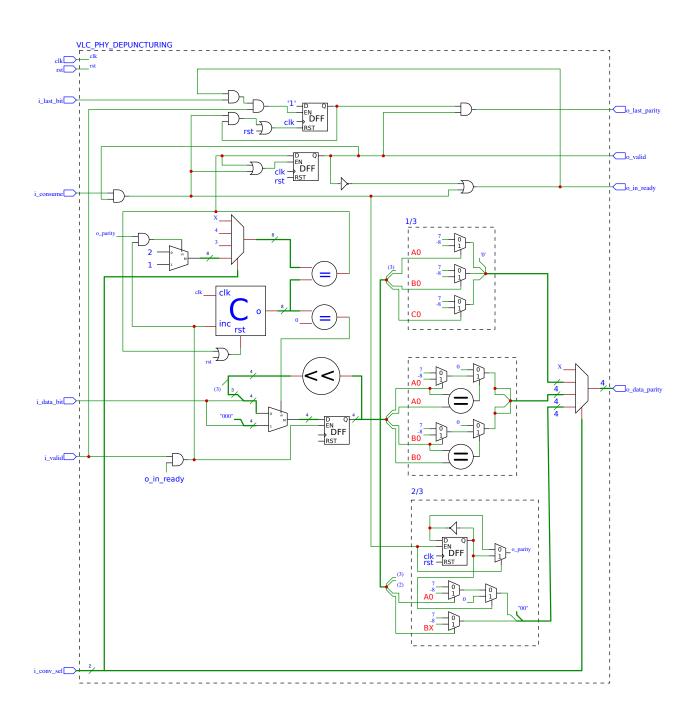

| Figure 67 – | Depuncturing of parity bits for rate conversion from $1/3$ to $1/4$ and $2/3$                                                                                                           |

|             | described in section 4.4.7.1. $\ldots$ 136                                                                                                                                              |

| Figure 68 – | Core cell types in TCB018GBWP7T [57]                                                                                                                                                    |

| Figure 69 – | Prefix Code Descriptions of Combinational Elements [57]                                                                                                                                 |

| Figure 70 – | Prefix Code Descriptions of Special Function Cells [57]                                                                                                                                 |

# List of Tables

| Table 1 –   | General FEC IP Core metrics                                                                    | 79  |

|-------------|------------------------------------------------------------------------------------------------|-----|

| Table 2 $-$ | Total number of data path connections (encoder + decoder) for each                             |     |

|             | <i>MCS_ID</i>                                                                                  | 84  |

| Table 3 $-$ | System requirements for VLC_PHY_FEC_CONTROLLER                                                 | 84  |

| Table 4 –   | Resource usage summary for the FEC IP in $5$ CGXFC5C6F27C7N                                    | 93  |

| Table 5 $-$ | Standard cell report summary for the FEC IP using TCB018GBWP7T .                               | 94  |

| Table 6 –   | Standard cell report summary for the FEC IP using GSC 3.0v library $\therefore$                | 94  |

| Table 7 $-$ | Description of the selected IPs for the comparison analysis                                    | 95  |

| Table 8 –   | Standard cell report summary for the selected IPs using GSC 3.0v library                       | 95  |

| Table 9 $-$ | Resource usage by instance for the FEC IP in $5$ CGXFC5C6F27C7N                                |     |

|             | (percentage number in parenthesis)                                                             | 96  |

| Table 10 –  | Area by instance for the FEC IP in TCB018GBWP7T (percentage                                    |     |

|             | number in parenthesis) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 97  |

| Table 11 –  | Memory utilization percentage for the FEC IP in $5$ CGXFC5C6F27C7N                             |     |

|             | and TCB018GBWP7T                                                                               | 97  |

| Table 12 –  | 12 topmost critical path for the FEC IP in 5CGXFC5C6F27C7N $~$                                 | 99  |

| Table 13 –  | 12 topmost critical path for the FEC IP in TCB018GBWP7T $\ldots \ldots 1$                      | 00  |

| Table 14 –  | Power consumption (in $mW$ ) for 5CGXFC5C6F27C7N by varying the                                |     |

|             | default toggle rate of all FEC IP signals                                                      | .04 |

| Table 15 –  | Power consumption (in $mW$ ) for TCB018GBWP7T by varying the static                            |     |

|             | probability of FEC IP signals                                                                  | 04  |

| Table 16 –  | Group IDs and their related MCS IDs and waveform length for the                                |     |

|             | original frame of 63B (in cycles)                                                              | 05  |

| Table 17 –  | Dynamic power consumption (in $mW$ ) for 5CGXFC5C6F27C7N based on                              |     |

|             | a typical VCD activity of each operating mode group using vlc_phy_fec $\hfill \label{eq:vcd}$  |     |

|             | as encoder                                                                                     | .07 |

| Table 18 –  | Dynamic power consumption (in $mW$ ) for 5CGXFC5C6F27C7N based on                              |     |

|             | a typical VCD activity of each operating mode group using vlc_phy_fec                          |     |

|             | as decoder                                                                                     | .07 |

| Table 19 –  | Dynamic power consumption (in $mW$ ) for TCB018GBWP7T based on                                 |     |

|             | a typical VCD activity of each operating mode group using vlc_phy_fec $\_$                     |     |

|             | as encoder                                                                                     | 08  |

| Table 20 –  | Dynamic power consumption (in $mW$ ) for TCB018GBWP7T based on                                 |     |

|             | a typical VCD activity of each operating mode group using vlc_phy_fec $\_$                     |     |

|             | as decoder                                                                                     |     |

| Table 21 –  | Latency violations for TCB018GBWP7T (ASIC)                                                     | 13  |

| Table 22 – Latency violations for 5CGXFC5C6F27C7N (FPGA)                            |

|-------------------------------------------------------------------------------------|

| Table 23 $-$ Latency, data rate and throughput of all IEEE 802.15.7 operating modes |

| for encoder and decoder portions on $5$ CGXFC5C6F27C7N (FPGA) and                   |

| TCB018GBWP7T (ASIC)                                                                 |

### Acronyms

- $ABV\,$  Assertion-Based Verification.

- AC Alternating Current.

- ACS Add-Compare-Select.

- ADC Analog-to-Digital Converter.

- ALM Adaptative Logic Module.

- ALUT Adaptive Look-up Table.

- ASIC Application Specific Integrate Circuits.

- BCH Bose and Ray-Chaudhuri.

- $BER\,$  Bit Error Rate.

- BM Branch Metric.

- CAGR Compound Annual Growth Rate.

- $CC\,$  Convolutional Codes.

- CCA Clear Channel Assessment.

- CD Compact Disk.

- CDR Clock and Data Recovery.

- CEx Counter Example.

- CMOS Complementary Metal Oxide Semiconductor.

- CoI Cone of Influence.

- CONN Connectivity.

- COTS Commercial Off-The-Shelf.

- CPU Central Processing Unit.

- CRC Cycle Redundancy Check.

- CS Compensation Symbols.

- CSK Color Shift Keying.

- CSV Comma-Separated Values.

- DAC Digital-to-Analog Converter.

- DC Direct Current.

- DDR Double Data Rate.

- DME Device Management Entity.

- $DS\,$  Data Subframe.

- DSP Digital Signal Processor.

- DUT Design Under Test.

- $DVD\,$ Digital Versatile Disk.

- Eb/N0 Energy per Bit to Noise Power Spectral Density Ratio.

- ECC Error Correcting Code.

- $EDA\,$  Electronic Design Automation.

- FEC Forward Error Correction.

- $FLP\,$  Fast Locking Pattern.

- FPGA Field Programmable Gate Array.

- FSM Finite State Machine.

- FSO Free-Space Optical.

- FV Formal Verification.

- G Groups.

- GF Galois Field.

- GP Generator Polynomial.

- GPIO General Purpose Input/Output.

- GPL General Public License.

- $GSC\,$  Generic Standard Cell.

- HCS Header-Check Sequence.

- HDL Hardware Description Language.

- HPF High-Pass Filter.

- I/O Input/Output.

- IC Integrated Circuit.

- ID Identifier.

- IoT Internet of Things.

- *IP* Intellectual Property.

- ISO International Organization for Standardization.

*IWLS* International Workshop on Logic and Synthesis.

JEITA Japan Electronics and Information Technology Industries Association.

- LAB Logic Array Block.

- $LD\,$  Laser Diodes.

- LDPC Low-density parity-check.

- LED Light-Emitting Diode.

- LiFi Light-Fidelity.

- LLC Logic Link Control.

- LoS Line of Sight.

- LPDDR Low-Power Double Data Rate.

- LUT Look-up Table.

- LVDS Low-voltage Differential Signaling.

- $MAC\,$  Medium Access Control.

- MCS Modulation and Coding Scheme.

- $MIT\,$  Massachusetts Institute of Technology.

- MLAB Memory Logic Array Block.

MTC Machine Type Communication.

- NMOS N-type Metal-Oxide-Semiconductor.

- OCC Optical Camera Communication.

- OFDM Orthogonal Frequency Division Multiplexing.

- OOK On-Off Keying.

- OSI Open System Interconnection.

- OWC Optical Wireless Communications.

- P/S Parallel/Serial.

- PCB Printed Circuit Board.

- PCI Peripheral Component Interconnect.

- PD Physical-layer Data.

- PHR Physical-layer Header.

- PHY Physical.

- PIB Physical-layer personal-area-network Information Base.

- PLME Physical-layer Management Entity.

- PM Path Metric.

- PMOS P-type Metal-Oxide-Semiconductor.

- PPDU Physical-layer Data Unit.

- ${\cal PS}\,$  Parallel-to-Serial.

- $PSDU\,$  PHY Service Data Unit.

- RAM Random-Access Memory.

- RF Radio Frequency.

- RIFS Reduced Interframe Space.

- *RISC* Reduced Instruction Set Computer.

- RLL Run-Length Limit.

- ROM Read-Only Memory.

- $RS\,$  Reed-Solomon.

- RTL Register Transfer Level.

- S/P Serial/Parallel.

- SAP Service Access Point.

- SDC Synopsis Design Constrains.

- SDR Software Defined Radio.

- SHR Synchronization Header.

- SIFS Short Interframe Space.

- SNR Signal to Noise Ratio.

- SoC System-on-Chip.

- $SP\,$  Serial-to-Parallel.

- SPI Serial Peripheral Interface.

- SRAM Static Random-Access Memory.

- SSCS Service-Specific Convergence Sublayer.

- STA Static Timing Analysis.

- SVA System Verilog Assertions.

- TDP Topology Dependent Pattern.

- TIA Trans-Impedance Amplifier.

- $TSMC\,$  Taiwan Semiconductor Manufacturing Company.

- UPF Unified Power Format.

- $USB\,$  Universal Serial Bus.

- USRP Universal Software Radio Peripheral.

- VCD Value Change Dump.

- VLC Visible Light Communication.

$VPAN\,$  Visible-light communication Personal Area Network.

- VPPM Variable Pulse Position.

- WiFi Wireless Fidelity.

- WPAN Wireless Personal Area Network.

- $WQI\,$  Wavelength Quality Indication.

# 1 Introduction

The demand for wireless communication has been imposed by the increasing number of mobile devices which require Internet connection and the strict data throughput requirements of their latest applications. As proof of that, a study carried out in 2017 [1] estimated that the Compound Annual Growth Rate (CAGR) of wireless traffic has been 60% during the last ten years. Moreover, if the same pace is maintained for the next two decades, the bandwidth request would rise by 12000 times if the same spectrum efficiency is assumed [2]. The expectations regarding Internet of Things (IoT) and Machine Type Communication (MTC) technologies indicate that such trend is realistic. Radio Frequency (RF) spectrum used by Wireless Fidelity (WiFi) has become unable to address the next mobile data traffic demands [3].

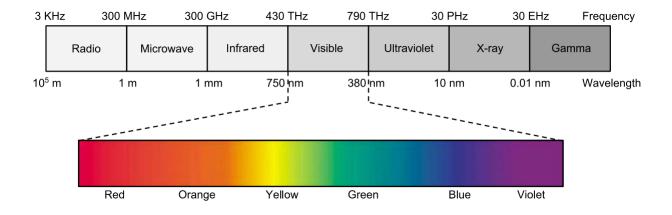

The aggressive exploration of spatial reuse has been the main approach adopted to mitigate the spectrum shortage issue, and it caused a massive shrinkage of cell sizes in cellular communication. For instance, the cell radius in 2G systems was 35 km, whereas it is expected 25 m for 5G to achieve higher data densities. However, this strategy is bound by infrastructure costs for connecting all access points to the core network and the augment of intra-cell interference with shorter cell radius [2]. Hence, the exploration of high frequency spectra will play a major role to meet the next requirements of mobile industry. Visible light spectrum (Fig. 1) has gained attention by the academic community since its use as communication medium - known as Visible Light Communication (Visible Light Communication (VLC)) - could abruptly increase data traffic capacity. Speeds around 100 Gbps have been demonstrated by academic researches [4, 5]. VLC poses as a reasonable candidate for being part of next generations of mobile services due several aspects:

- Energy-efficient Light-Emitting Diode (LED) light bulbs have been widely adopted to replace incandescent and fluorescent lamps. They could easily provide illumination and data communication functions.

- Visible light spectrum is license-free.

- Improvement in data densities around three orders of magnitude in comparison to current RF technologies [6].

- Unlike RF, visible light cannot pass through walls, and this intrinsic feature enhances physical layer security.

- It is allowed to be used in environments where RF is banned (i.e petrochemical plants and oil platforms) [2].

• It can be employed as a complement to WiFi technologies without major issues [7].

Despite of several advantages, VLC faces some challenges for its wide deployment in wireless communication systems. According to the Friis free space equation, higher frequencies mean path loss raises in electromagnetic wave propagation [8]. Hence, VLC systems require enhancements in the probability of Line of Sight (LoS). Moreover, visible light source used for communication are subjected to interference from sunlight and other light sources. Therefore, VLC transceivers must be designed with coding techniques that are able to mitigate possible errors occurred in the communication channel.

Figure 1 – Visible light in electromagnetic spectrum scale ([9], p. 2048)

#### 1.1 VLC: Related Terminologies and Standards

Technically, VLC categorizes any type of communication where data is transmitted via visible spectrum, which contains wavelengths ranging from 380 nm to 750 nm. A requirement present in VLC is that data transfer should not modify light source aspects perceived by human vision such as brightness and flickering. There are other terminologies that are similar to VLC, but they have some differences:

- Optical Wireless Communications (OWC): It encompasses the whole optical band infrared, visible, and ultraviolet for wireless communication [10]. Then, VLC is a subset of OWC.

- Free-Space Optical (FSO) Communication: It is considered as a specialization of OWC in which it focuses on high data rate communication between two fixed points over distances up to several kilometers. Transmission occurs in a medium without barriers and very narrow laser beams are used in FSO systems [11].

• Light-Fidelity (LiFi): It is not restricted to visible light, and it also accepts infrared and ultraviolet. LiFi provides a complete proposal of a wireless networking system, which includes a bi-directional multiuser communication with high data rate and multiple access points to enable full user mobility [3]. This term arises to contrast with original stardards and systems elaborated for VLC, which has been conceived as a point-to-point data communication technique with lower speeds.

The standardization process for VLC is in continuous progress. The first initiative was carried out in 2003 by the VLC Consortium in Japan. It resulted in two standards for VLC systems included in Japan Electronics and Information Technology Industries Association (JEITA): CP-1221 and CP-1222 [12]. In 2011, IEEE 802.15.7 [13] (Short-Range Wireless Optical Communication Using Visible Light) was released, and it specifies Physical (PHY) and Medium Access Control (MAC) layers for VLC. This first IEEE standard for VLC encompasses thirty operating modes among three PHY layers with On-Off Keying (OOK), Variable Pulse Position (VPPM), and Color Shift Keying (CSK) as modulation scheme options. In order to cope with LED Identification (LED-ID), Optical Camera Communication (OCC) and High Rate Power Distance Communication, IEEE 802.15.7m was launched in 2014 with three new PHY modes with several modulation schemes [14, 15]. After that, the standardization for High Rate Power Distance Communications has been moved to IEEE 802.15.7 (Multi-Gigabit/s Optical Wireless Communications), which added two new Orthogonal Frequency Division Multiplexing (OFDM)-based PHY modes. Recently, IEEE 802.11bb has been created to deal with light-based systems, aiming to define a single ecosystem for chipset vendors, specify LiFi network infrastucture, and establish a cooperation between LiFi with WiFi standards [16].

#### 1.2 Forward Error Correction (FEC)

FEC defines a set of error control techniques targeted to improve the capacity of a transmission channel by incorporating to the source data some designed redundant information [17]. It is employed in applications in which re-transmission is costly or impossible such as satellite and broadcast communications. The FEC encoding process builds an output codeword that is characterized by some specific rule which restricts their possible values. As a consequence, the FEC decoding process relies on such rule to extract the most probably correct codeword from the received data. The methods applied for FEC fall into two major categories:

• Block codes: Data stream is broken up into a series of fixed-size packets of n bits in length. If k bits are allocated to the original source data where k < n, then the code rate is defined by n/k, which is commonly represented by the notation (n, k). Block

codes are implemented by hard-decision algorithms since their produced results are based on data input with strict values ('0' or '1' in binary notation) [18]. Examples of this category are Hamming, Bose and Ray-Chaudhuri (BCH), Reed-Solomon (RS) and Low-density parity-check (LDPC) codes.

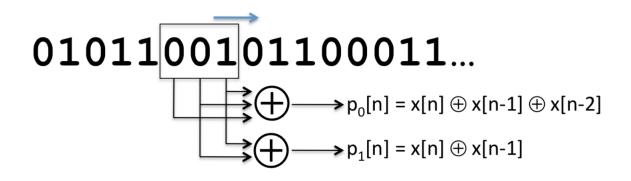

Convolutional Codes (CC): Data stream is treat as a string of consecutive bits constrained by a maximum length of K bits [19]. The encoder scheme is conceived by m shift registers, and the output is generated by a linear combination of selected shift register outputs which maps to a generator polynomial [17]. They are characterized by a coding rate of k/n, which means that n output bits will be produced for each k input bits. Viterbi algorithm is the most common decoding methodology. It is based on the maximum likelihood decoding technique and operates with hard or soft-decision methods [18]. Soft decision algorithms use a multi-bit quantization to represent the probability of a single data bit be '0' or '1'.

Conventional Error Correcting Code (ECC) algorithms may be used in VLC systems. IEEE 802.15.7 prescribes three operational ECC blocks for its FEC system which have been widely used in other applications: RS codes, Interleaver, and CC. The main particularity of VLC is that the light source used to transmit data should not flicker or change its intensity; however, these ECC methods employed in the FEC system does not guarantee an even distribution of 0's and 1's for the encoded frame [20]. Hence, it may cause disturbances in the light source that are perceived by human vision depending on the chosen modulation scheme. IEEE 802.15.7 mitigates them by using Compensation Symbols (CS) within the encoded frame and Run-Lenght Limit (Run-Length Limit (RLL)) coding strategies that balances the distribution of 0s and 1s within the encoded bitstream.

#### 1.3 Motivation and Goals

VLC is a topic that has gained attention in academic and corporate fields because of the incipient RF spectrum crunch in wireless communication. Many startups like pure LiFi, Lucibel, vlncomm, OLEDCOM, and others have been established to develop dedicated VLC and LiFi systems [21]. Large companies such as Signify, General Electric and Panasonic have also invested in this area. Most frameworks for VLC are implemented in software and installed into embedded platforms. They are more prototypes than final user solutions since PHY layers should have a dedicated implementation in hardware to meet throughput requirements. For IEEE 802.15.7, there are very few works on developing a digital system for PHY layer.

The goal of this master thesis is to explore the PHY layer of IEEE 802.15.7 by developing a digital system for its FEC, which is the most complex block of that layer.

In order to contextualize the FEC for IEEE 802.15.7, the main relevant aspects of the standard for it are covered in this document and related works are analyzed. The deliverable of this work is an open access Register Transfer Level (RTL) Intellectual Property (IP) of the FEC specified in IEEE 802.15.7.

IEEE 802.15.7 is the starting point to understand basic premises of a PHY layer for VLC systems. That is reason for sticking to this standard instead of exploring the latest updates for VLC standards, which still require some level of maturation. Moreover, the operational blocks of the FEC system implement well known algorithms used in other applications or standards. They were designed to be parameterizable, which enables using them in other contexts that require configuration setups other than the ones specified in IEEE 802.15.7.

This work covers implementation steps that are common in every project of a RTL IP. The resulting Hardware Description Language (HDL) files adopted certain coding style, signal name convention, and sub-block reuse. The verification methodology of the developed IP has also been detailed in this thesis. Performance metrics of the FEC system are collected for Field Programmable Gate Array (FPGA) and Application Specific Integrate Circuits (ASIC) flows and analyzed in this work. Such results are important to assess the proposed IP and certify that there is not any architectural flaws in its design.

The result of this master thesis is the first step to enable an open IP for IEEE 802.15.7 PHY layer, which is something that is not available to the academic community yet. The FEC is the most complex system within this PHY layer, then the effort required to obtain an end-to-end solution for IEEE.802.15.7 will be significantly lower after this work. VLC is an emerging research field that lacks an adequate digital framework for its PHY layer, which is a prerequisite for any feasible network connection. Several subsequent projects are enabled by this master thesis, and they present different levels of complexity and activity types.

## 1.4 Thesis Roadmap

This master thesis is organized as follows: Chapter 2 elucidates key aspects of the IEEE 802.15.7 PHY layer that are required to comprehend the developments of this work; Chapter 3 is literature review related works, which provides a better picture about the novel contribution of this work; Chapter 4 carries out a detailed analysis of the RTL architecture of the proposed digital system to perform FEC; Chapter 5 analyzes the results the implemented RTL IP; and Chapter 6 delineates the future works and presents the conclusions of this master thesis.

# 2 IEEE 802.15.7: Guided Review

This chapter reviews aspects of IEEE 802.15.7 that are relevant for understanding architectural implications for PHY layer design and implementation details of the FEC specified by the standard. It provides a guided overview of IEEE 802.15.7 based on what is required to understand the development of this master thesis.

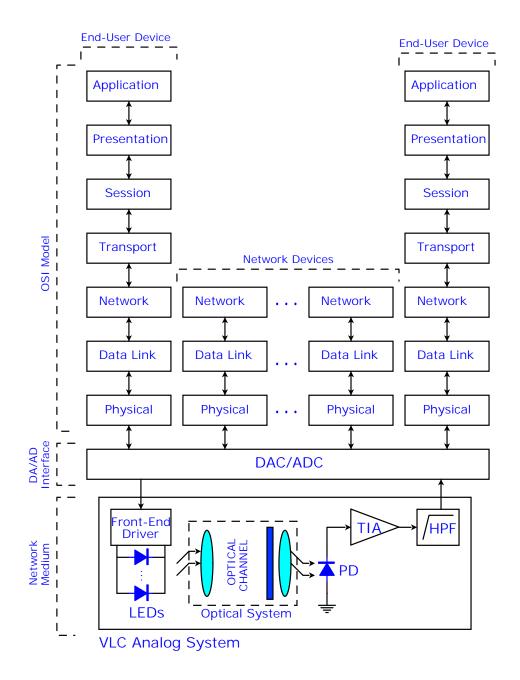

Before exploring the key aspects of IEEE 802.15.7, it is relevant to cover the general process to exchange data via VLC in order to understand where the standard fits in. Fig. 2 depicts all communication blocks required to interconnect to end-user devices in the network using VLC. The Open System Interconnection (OSI) model is a International Organization for Standardization (ISO) standard released in 1979 responsible for establishing a unified communication architecture based on seven well-defined layers. Such layered model is a reference until today because it simplifies the understand of the network architecture, creates behavioral domains that facilitate implementation and troubleshooting of the network and guarantees better consistency in functions and protocols [22]. Hubert Zimmermann, member of the OSI standardization group, provides an overview of the seven layers of the OSI model in [23]:

- Application serves the end user by providing protocols appropriate to application management tasks (e.g initiate, maintain, and terminate connections for data transfer).

- *Presentation* provides the set of services for the management, display, and control of structured data used by *Application* layer.

- Session establishes an administration service mechanism to (un)bind presentation entities and controls their data exchange.

- Transport provides an universal transport service in a reliable and cost-effective way.

- *Network* allows functional and procedural means to exchange network service data units considering routing and switching aspects of the network connection.

- *Data Link* provides means to establish, maintain and release data links between network entities.

- *Physical* offers mechanical, electrical, functional, and procedural characteristics to establish maintain, and release physical connections between data link entities.

Figure 2 – Communication blocks required to transfer data between two end-user devices.

IEEE 802.15.7 covers *Data Link* and *Physical* layers of the OSI model as they are tied to the characteristics of the network medium used for data transfer. A Digital-to-Analog Converter (DAC) or a Analog-to-Digital Converter (ADC) are required to bind the digital blocks that implement the OSI model and the analog transducer system. The VLC analog system requires LEDs, controlled by a front-end driver circuit that implements a transconductance amplifier, to transmit data and a Physical-layer Data (PD) to detect the light source, which demands a Trans-Impedance Amplifier (TIA) and a High-Pass Filter (HPF) to amplify its voltage and remove low-frequency components of the received signal.

Also, an optical system (lens and filters) may required to adjust the light beam in order to enhance optical communication performance. Between the end-user devices there might be some network devices (e.g repeaters, hubs, switches, and routers) used to transport data transferred by the end-user devices. They are devices that implements at most the three lowest layers of the OSI model and may require other network mediums (e.g optical fiber) that are omitted in Fig. 2.

A key aspect in VLC is that the data transmitted by LEDs and Laser Diodes (LD) cannot cause any light source disturbances that may be detected by the human eye. Hence, IEEE 802.15.7 introduces the concept of Visible-light communication Personal Area Network (VPAN), which is a branch of Wireless Personal Area Network (WPAN). This specialization is required because it aims to merge lighting and data communication functions on the same device, which brings up new requirements such as dimming and visibility support that impact the specification of *Data Link* and *Physical* layers for VLC.

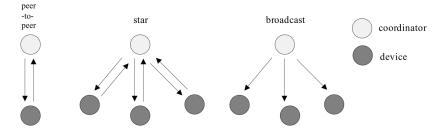

# 2.1 Topologies Types

VPAN defines three topologies: peer-to-peer, star, and broadcast (Fig. 3). There is always a VLC device in the network which assumes the coordinator role, which manages the VPAN and is usually always powered on. Each device has a unique 64-bit address, which may be shortened to 16-bit address when it is associated with a coordinator. In peer-to-peer topology, the coordinator role is assigned to the first device that starts to transmit data. Networks structured in a star topology are identified by a VPAN number not used by any other surrounding VPAN networks. This Identifier (ID) is held by the coordinator, which allows newcomer devices to join the network. Broadcast topology does not require a network formation, and transmissions of unidirectional signals may be captured by any device in their range.

Figure 3 – Network topologies in IEEE 802.15.7 ([13], p. 6)

## 2.2 Architectural Aspects

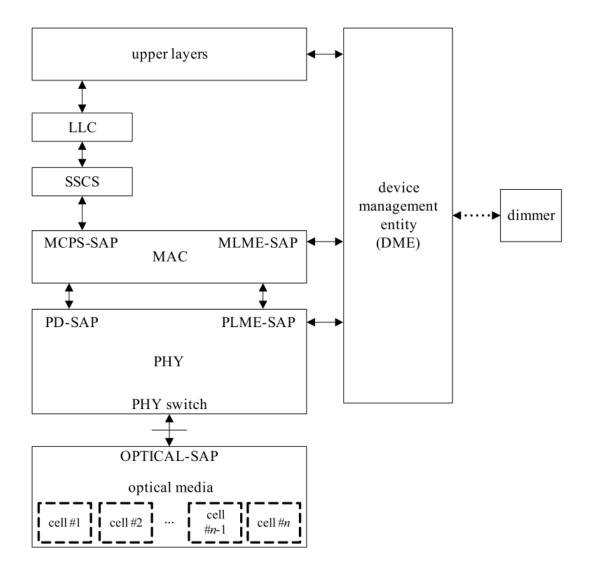

The system architecture for IEEE 802.15.7 is organized in layers and sublayers that offers services to higher layers (Fig. 4), and such arrangement is compliant with the OSI model. The standard specifies the PHY layer and the MAC sublayer with its accessor Service-Specific Convergence Sublayer (SSCS). Logic Link Control (LLC) layer is defined by IEEE 802.2, and the upper layers are not covered by IEEE 802.15.7. The Device Management Entity (DME) is a control interface that sets up dimmer related attributes in MAC and PHY layers such as the selection of optical light sources and photodetectors. These devices are identified as cells, and they communicate with the PHY switch via OPTICAL Service Access Point (SAP) interface, which is not specified by the standard.

The implementation of the VPAN architecture should consist of a hardwarefirmware co-design. PHY layer is usually implemented in hardware since it deals with time-critical signal processing functions. MAC layer should be implemented as a firmware, though, because it implements a complex structure of protocol logics, and a software approach facilitates its realization. However, it is required to implement a MAC driver that communicates to the PHY layer using the interfaces provided by PD-SAP and Physical-layer Management Entity (PLME)-SAP. As DME interacts with many layers of the network model, it should be implemented similarly to MAC. Finally, a DAC/ADC must be placed between the PHY switch and the OPTICAL-SAP because this is the boundary between analog and digital worlds.

## 2.3 PHY Layer

The following functions are assigned to PHY layer:

- Activation and deactivation of the VLC transceiver

- Wavelength Quality Indication (WQI) for received frames

- Channel Selection

- Data transmission and reception

- Error Correction

- Frame Synchronization

PHY layer in IEEE 802.15.7 supports three PHY layers, which are characterized by their defined operating modes (section 2.3.1). Each one is focused on a different communication scenario:

Figure 4 – VPAN device architecture ([13], p.8).

- PHY I: Intended for outdoor usage with low data rate applications (hundreds of kb/s).

- PHY II: Intended for indoor usage with moderate data rate applications (tens of Mb/s).

- PHY III: Indicated for applications using color-shift keying (CSK) that have multiple sources and detectors (tens of Mb/s).

As highlighted by Fig. 5, PHY I and PHY II occupy different spectral regions in the modulation-domain spectrum, and Frequency Division Multiplexing (FDM) mechanism may be used as a coexistence mechanism for both PHY layers. The same scenario is applicable for PHY I and PHY III. For PHY II and PHY III, their modulation frequencies

overlap, then PHY III is able to detect PHY II communication to avoid such prohibitive overlap.

## 2.3.1 Operation Modes

PHY I, PHY II and PHY III specify nine, fourteen, and seven operating modes with data rates ranging from 11.67 kb/s to 96 Mb/s. Three modulation schemes are used: OOK, VPPM, and CSK. OOK is the simplest modulation method, where light source in 'ON' and 'OFF' state represents '1' and '0' logic values (Fig. 6a). VPPM models logic values by the position of the pulse within the optical clock cycle, and its variable pulse provides an inherent dimming control mechanism (Fig. 6b). CSK codes information bits into different color wavelengths and requires three light sources to emit red, green, blue colors. IEEE 802.15.7 specifies seven band ranges to encode data (Fig. 6c) with constellations of sizes 4, 8, and 16 symbols.

The RLL techniques are applied in PHY I and PHY II and aim to bound the length of repeated bits in a stream, and it eases clock recovery at the receiver. They also help in Direct Current (DC) balance and light flicker mitigation. Manchester mode encodes logic values into transitions '0' to '1' and '1' to '0', being a self-clocking signal without a DC component (Fig. 7a). Because of that, data rate is reduced by two and light source brightness is constant at 50%. CSs are required then to adjust the source light brightness to the desired intensity. 4B6B mode converts 4 to 6 bits, where the most uneven bit value distributions for 6-bit words are excluded (Fig. 7b). 8B10B uses the same approach of 4B6B, but it converts 8 to 10 bits.

Multiple optical clock rates are provided to allow the application of a broader class of optical transmitters. MAC layer defines an optical clock-rate selection procedure during device discovery phase. The clock rate does not change during the transmission of different portions of the PHY frame: the preamble, used to synchronize the receiver with the clock rate required by the incoming message, the header, which contains fields required to configure the PHY device to receive the message, and the payload, which is the

Figure 6 – Modulation schemes present in IEEE 802.15.7 PHY layers: OOK (a), VPPM (b), and CSK (c) ( [24], p. 42 for (a) and (b) [13], p. 254 for (c))

Figure 7 – IEEE 802.15.7 RLL coding conversion examples ([24], p. 41).

message itself that is processed by the MAC layer. However, header should be sent at the lowest available data rate of the selected optical clock rate. Also, the preamble does not require any data encoding. The preamble and the header shall be transmitted using OOK.

Annex A summarizes the modulation and the RLLs techniques required by each operating mode in PHY I, II, and III (Fig. 56, 57, and 58). There are ten possible arrangements for FEC specified by the thirty operating modes. RS codes are used in all

PHY layers, and PHY I also counts on CC since it is potentially more exposed to channel interference. More explanation about RS and CC will be provided in the next chapters. The goal of this master thesis involves providing a digital system for IEEE 802.15.7 FEC that is able to harmonize all possible combinations for FEC present in the standard. The optical clock rate - the frequency at which the data is clocked out to the optical source - of each operating mode is a constrain which defines the minimum data rate for each arrangement required for the IEEE 802.15.7 FEC.

## 2.3.2 Frame Structure

All fields of PHY frame are presented in Fig.8. There are 5 major fields, and each composes a group of subfields.

#### 2.3.2.1 Synchronization Header (SHR)

This field used for synchronization of the optical clock at the receiver end. Fast Locking Pattern (FLP) is a variable sequence of alternate ones and zeros which is identified by the Clock and Data Recovery (CDR) circuit - the entry point for the incoming message at the receiver. Topology Dependent Pattern (TDP) is a pattern of 15 bits that identifies the network topology: only visibility, peer-to-peer, star, and broadcast. Four repetitions of this pattern are sent, and every subsequent repetition is inverted to provide DC balance.

#### 2.3.2.2 Physical-layer Header (PHR)

This field represents the PHY Header, which provides information to configure the VLC PHY device that is receiving the message. The first bit informs if 'Burst mode' is enabled. The subsequent three bits represent the 'Channel number' used in PHY III for CSK modulation. The subfield 'MCS ID' is a 6-bits representation for each Modulation and Coding Scheme (MCS) operating mode specified in Fig. 56, 57, and 58. The 'PSDU Length' is informed by a 16-bit word since the payload - PHY Service Data Unit (PSDU) - may assume maximum values (in bytes) of 1023 for PHY I or 65535 for PHY II and PHY III. The next bit informs if 'Dimmed OOK extention' is enabled, which basically determines the existence of the optional field. The 5 last bits are reserved for future use.

#### 2.3.2.3 Header-Check Sequence (HCS)

Every PHY header shall be protected with a 2 octet Cycle Redundancy Check (CRC).

#### 2.3.2.4 Optional Fields

As illustrated by Fig. 8, there are three possibilities for optional field. Tail bits shall be transmitted at the end of the PHY header whenever the selected operating mode uses CC in its FEC scheme. If 'Dimmed OOK extension' is enabled, then four more fields are added to set up the dimming mitigation support for OOK modulation. More information about them may be found in section 8.6.4 of IEEE 802.15.7. And 'Channel Estimation Sequence' is used by PHY III and discussed in section 12.9 of IEEE 802.15.7.

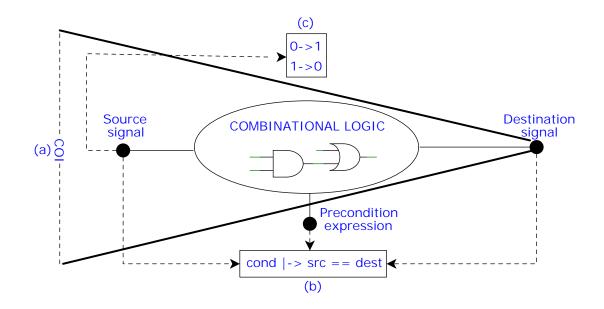

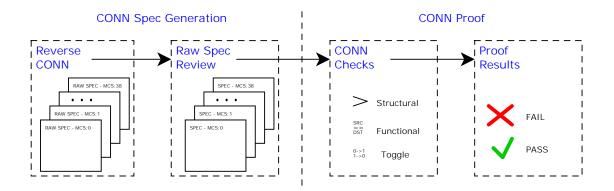

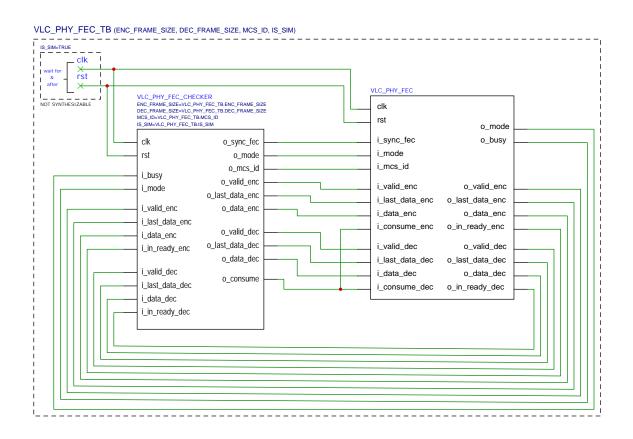

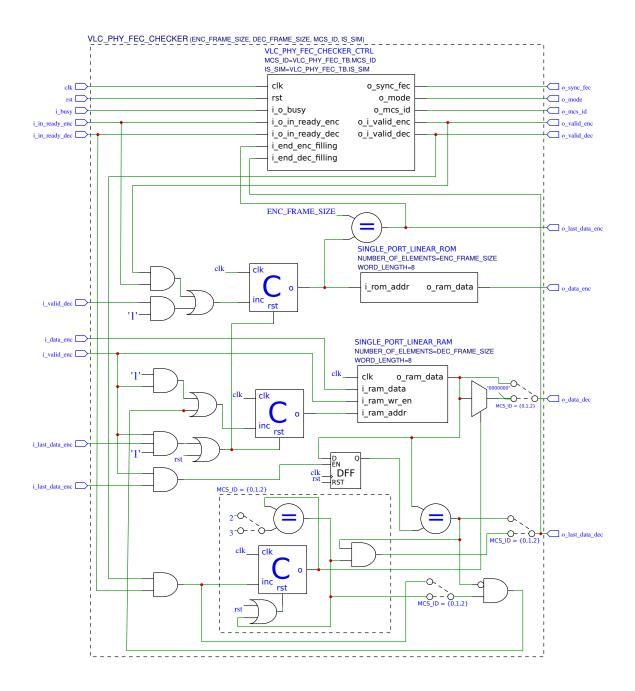

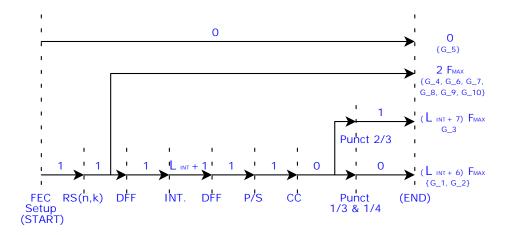

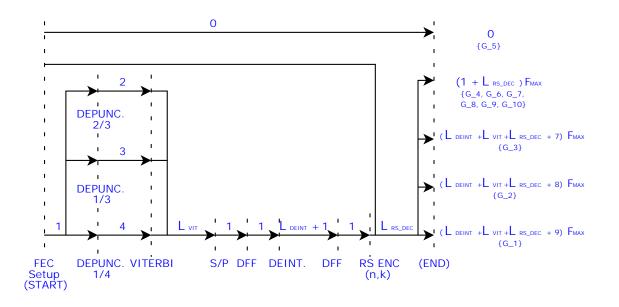

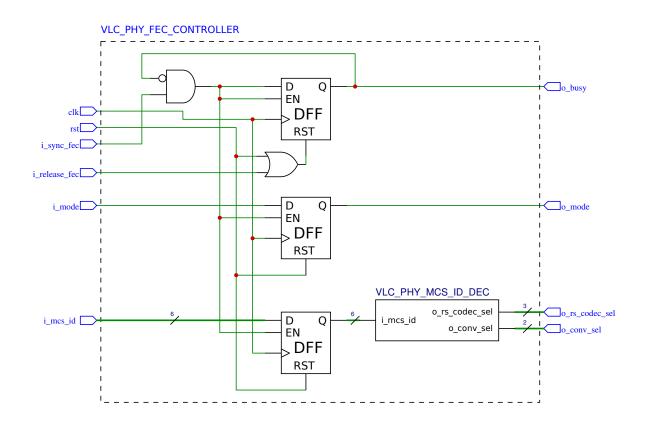

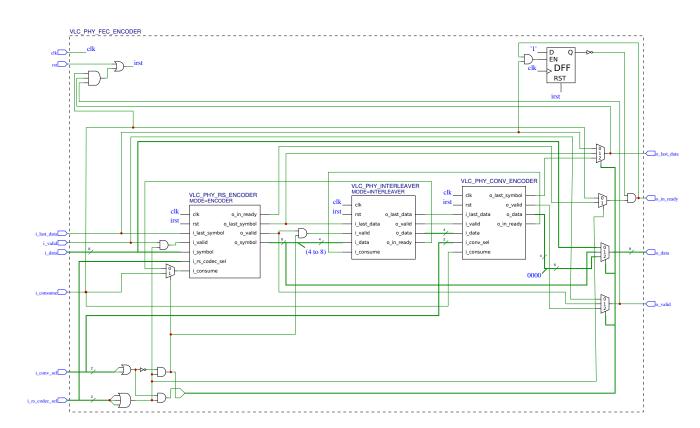

#### 2.3.2.5 PHY Service Data Unit (PSDU)