# Universidade Federal de Minas Gerais Escola de Engenharia Programa de Pós-Graduação em Engenharia Elétrica

# DESENVOLVIMENTO DE FERRAMENTAS COMPUTACIONAIS PARA A ANÁLISE DE PERDAS EM CONVERSORES ESTÁTICOS: APLICAÇÃO AO CÁLCULO DE RENDIMENTO DE UPSS TRIFÁSICAS DE DUPLA CONVERSÃO

**Anna Paula Leite Cota**

Belo Horizonte

## DISSERTAÇÃO DE MESTRADO Nº 932

DESENVOLVIMENTO DE FERRAMENTAS COMPUTACIONAIS PARA A ANÁLISE DE PERDAS EM CONVERSORES ESTÁTICOS: APLICAÇÃO AO CÁLCULO DE RENDIMENTO DE UPS'S TRIFÁSICAS DE DUPLA CONVERSÃO

Anna Paula Leite Cota

DATA DA DEFESA: 28/07/2016

### Universidade Federal de Minas Gerais

### Escola de Engenharia

## Programa de Pós-Graduação em Engenharia Elétrica

DESENVOLVIMENTO DE FERRAMENTAS COMPUTACIONAIS PARA A ANÁLISE DE PERDAS EM CONVERSORES ESTÁTICOS: APLICAÇÃO AO CÁLCULO DE RENDIMENTO DE UPS'S TRIFÁSICAS DE DUPLA CONVERSÃO

#### Anna Paula Leite Cota

Dissertação de Mestrado submetida à Banca Examinadora designada pelo Colegiado do Programa de Pós-Graduação em Engenharia Elétrica da Escola de Engenharia da Universidade Federal de Minas Gerais, como requisito para obtenção do Título de Mestre em Engenharia Elétrica.

Orientador: Prof. Porfírio Cabaleiro Cortizo

Coorientador: Prof. Paulo Fernando Seixas

Belo Horizonte - MG

Julho de 2016

C843d

Cota, Anna Paula Leite.

Desenvolvimento de ferramentas computacionais para análise de perdas em conversores estáticos [manuscrito] : aplicação ao cálculo de rendimento de UPSs trifásicas de dupla conversão / Anna Paula Leite Cota .- 2016.

174 f., enc.: il.

Orientador: Porfírio Cabaleiro Cortizo. Coorientador: Paulo Fernando Seixas.

Dissertação (mestrado) Universidade Federal de Minas Gerais, Escola de Engenharia.

Apêndices: f.169-174.

Bibliografia: f. 164-168.

1. Engenharia elétrica - Teses. 2. Sistemas ininterruptos de energia - Teses. I. Cortizo, Porfírio Cabaleiro. II. Seixas, Paulo Fernando. III. Universidade Federal de Minas Gerais. Escola de Engenharia. IV. Título.

CDU: 621.3(043)

"Desenvolvimento de Ferramentas Computacionais para a Análise de Perdas em Conversores Estáticos: Aplicação ao Cálculo de Rendimento de UPS's Trifásicas de Dupla Conversão"

#### **Anna Paula Leite Cota**

Dissertação de Mestrado submetida à Banca Examinadora designada pelo Colegiado do Programa de Pós-Graduação em Engenharia Elétrica da Escola de Engenharia da Universidade Federal de Minas Gerais, como requisito para obtenção do grau de Mestre em Engenharia Elétrica.

Aprovada em 28 de julho de 2016.

Por:

Prof. Dr. Porfírio Cabaleiro Cortizo

DELT (UFMG) - Orientador

Prof. Dr. Paulo Fernando Seixas DELT (UFMG) - Coorientador

Prof. Dr. Sidelmo Magalhães Silva DEE (UFMG)

Prof. Dr. Pedro Francisco Donoso Garcia

DELT (UFMG)

Eng. Msc. Paulo de Tarso Paixão Lopes (Engetron Ltda.)

Prof. Dr. Thiago Ribeiro de Oliveira DELT (UFMG)

hoiro de A

## **AGRADECIMENTOS**

Agradeço aos professores Porfirio Cabaleiro e Paulo Seixas, pela orientação, paciência e compreensão. À Engetron, pelo financiamento desta pesquisa e confiança. Aos engenheiros da Engetron, Wilton Padrão, Paulo de Tarso, Vinícius, Mário Henrique, Marcos Flávio e outros, pelo apoio técnico, receptividade e pelas orientações. À minha família, pelo apoio incondicional e pela ajuda persistente, muitas vezes não merecida. Em especial, à minha mãe, Cida, meu pai, Miguel e aos meus irmãos Carol, Breno e Dudu e à agregada, cunhada Débora, por me tolerarem e apoiarem todos os dias. Ao meu namorado, Renato, pelo carinho e cumplicidade e por ter preservado esse status, sem que eu fosse uma namorada dedicada e presente. Aos meus amigos (em especial, ao grupo das BPs do COLTEC, ao Túlio, à Bárbara e ao Luiz), que ainda se mantiveram ao meu lado, não obstante a minha ausência e negligência, enquanto eu redigia este trabalho. Aos parceiros do Grupo de Eletrônica de Potência (GEP), Welbert, Rafael (Jesus), Ana Carolina, Thiago (Banana), Thiago Ribeiro e outros, pela amizade, pelas inúmeras ajudas e conversas. Aos professores Lenin, Marcos Severo, Pedro Donoso, Braz Cardoso, Sidelmo, Selênio (in memoriam) pelas lições valiosas que não só me orientaram ao longo desta pesquisa, como também contribuíram para que eu optasse pela Eletrônica de Potência, ainda na Graduação. Ao professor Antônio Carlos Andrade, do Departamento de Engenharia Mecânica, pelas contribuições na fase de projeto do calorímetro. Meus agradecimentos a estes professores e aos meus orientadores também pela dedicação ao ofício de professor e pesquisador, apesar dos incontáveis entraves burocráticos e políticos. Aos parceiros do Mestrado, Nicole, Edmar, Rafael (Jesus), Allan, André Filipe, Victor e outros pelas discussões acaloradas e noturnas sobre os trabalhos das disciplinas de pós-graduação. Aos parceiros da Leme Engenharia, Isabela Metzker (Bolacha), Daniel Lavall, Daniel Pechir, Helena Botelho, Caroline Martins e Evandro Marzano, pela amizade e por terem permitido que a convivência com os estudos de transitórios eletromagnéticos e com o ATP fosse menos traumática. Ao Maurício, técnico do DELT, pela prestatividade e solicitude. À família do Renato, Iracema, Marcão, Gabriela, André Luiz, Arles, pela torcida. Ao meu exemplo de engenheira eletricista, Angélica Rocha, que como ninguém domina o tema de transformadores e transitórios eletromagnéticos e, ainda assim, não perde a humildade e o respeito ao próximo. À equipe do abnTFX2, por ter disponibilizado o template adotado neste trabalho.

Por fim, agradeço à Universidade Federal de Minas Gerais, a quem devo minha formação como técnica em Eletrônica, engenheira eletricista e agora, como mestre em Engenharia Elétrica.

## **RESUMO**

As UPSs (Uninterruptible Power Supplies) de dupla conversão são equipamentos que proveem a alimentação segura e sustentada de subsistemas com missão crítica, em que os distúrbios ou a interrupção no suprimento podem levar a perdas e danos. Esta dissertação objetiva comparar os rendimentos globais de UPSs trifásicas de dupla conversão nas topologias de dois níveis, com componentes de silício e de carbeto de silício (SiC) e de três níveis em arranjos NPC1 (Neutral-Point Clamped) e NPC2, com dispositivos de silício. A metodologia adotada se baseia na comparação de 80 projetos de UPSs de dupla conversão, com distintas especificações de tensão no barramento c.c., frequência de chaveamento e potência nominal. Para tanto, ferramentas de software com interface gráfica foram implementadas em MATLAB para estimar as perdas nos semicondutores e nos indutores dos filtros LCL de entrada e LC de saída da UPS. As simulações das UPSs foram conduzidas no ambiente MATLAB/Simulink e incluem o controle dos estágios inversor e retificador. Para fins de validação experimental das estimativas teóricas de perdas, um protótipo de um conversor buck de 5,5 kW foi construído e a potência dissipada neste circuito foi medida via wattímetro digital. Em seguida, um protótipo simples e de baixo custo de um calorímetro indireto série foi desenvolvido, para que as incertezas associadas às leituras de perdas fossem reduzidas. Os resultados de simulação indicam que a topologia NPC1 exibe maior rendimento global dentre as UPSs com componentes de silício, para a maior parte dos projetos de UPS avaliados. Ademais, as UPSs com SiC superam o desempenho da maioria das variações de silício em análise, o que acena para a viabilidade dos componentes de SiC para estas aplicações. Os resultados experimentais apontam para a concordância entre as estimativas de perdas e as medições via wattímetro. A efetividade do protótipo de calorímetro indireto série para a medição de perdas é demonstrada em ensaios com resistores de potência. Por fim, as técnicas propostas para a avaliação teórica de perdas podem ser estendidas para qualquer conversor estático e podem orientar o projeto de equipamentos mais eficientes e com maior densidade de potência.

Palavras-chave: UPS. Conversores estáticos. Cálculo de Perdas. Carbeto de silício. Calorímetro.

## **ABSTRACT**

Double-conversion UPSs (Uninterruptible Power Supplies) are devices that provide safe and continuous supply to mission-critical systems, in which disturbances or interruptions in power supply can lead to losses or damages. This thesis aims to compare the energy efficiency performance of three-phase double-conversion UPS in two-level topologies, with silicon and silicon carbide (SiC) devices, and in three-level topologies in NPC1 (Neutral-Point Clamped) and NPC2 configurations, with silicon power modules. The adopted methodology is based on the comparison of 80 designs of double-conversion UPS, with several values of d.c. bus voltages, switching frequencies and rated power. In order to accomplish this goal, software tools with graphical interface were implemented in MATLAB, for semiconductor losses estimation and for inductor losses calculation in input and output LC and LCL filters. UPS simulations were performed in MATLAB/Simulink and include the inverter and rectifier control. For experimental validation of the theoretical results, a circuit of a 5.5 kW buck converter was built and power losses measurements were conducted with a digital wattmeter. Then, a simple and low cost indirect series calorimeter prototype was developed, in order to reduce the uncertainties in power losses measurement. Simulation results show that NPC1 topology exhibits the highest global efficiency among the silicon based UPSs, in most UPS designs. Furthermore, the SiC based UPSs mostly overcome the performance of silicon based UPSs, which shows the competiveness of SiC devices for UPS applications. Experimental results prove the agreement between theoretical and measured results using digital wattmeter. Preliminary tests with power resistors demonstrate the effectiveness of the indirect series calorimeter prototype. Lastly, the proposed techniques for losses evaluation could be extended for any power converter and could enhance equipment design regarding energy efficiency and power density.

Keywords: UPS. Power converters. Power losses calculation. Silicon carbide. Calorimeter.

# LISTA DE ILUSTRAÇÕES

| 1.1  | Topologias trifásicas analisadas                                                 | 6  |

|------|----------------------------------------------------------------------------------|----|

| 2.1  | Causas de falhas e custos da indisponibilidade de sistemas críticos              | 9  |

| 2.2  | Módulos básicos de uma UPS                                                       | 9  |

| 2.3  | Classificação das UPSs                                                           | 10 |

| 2.4  | Tipos de UPS rotativas.                                                          | 11 |

| 2.5  | Diagrama esquemático de uma UPS híbrida                                          | 12 |

| 2.6  | Diagrama esquemático de uma UPS offline                                          | 13 |

| 2.7  | Diagrama esquemático de uma UPS line-interactive                                 | 15 |

| 2.8  | Diagrama esquemático de uma UPS de dupla conversão                               | 16 |

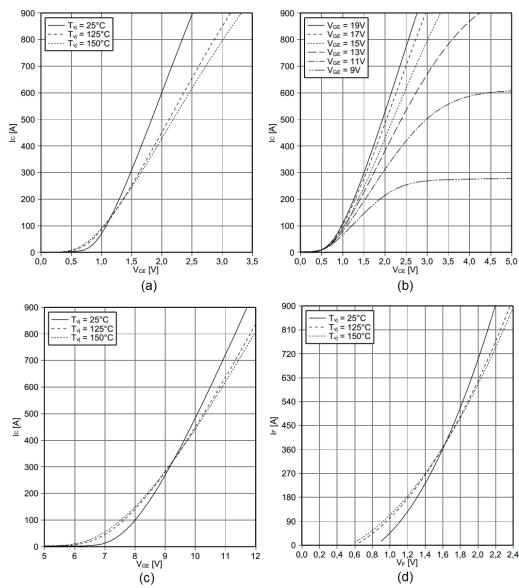

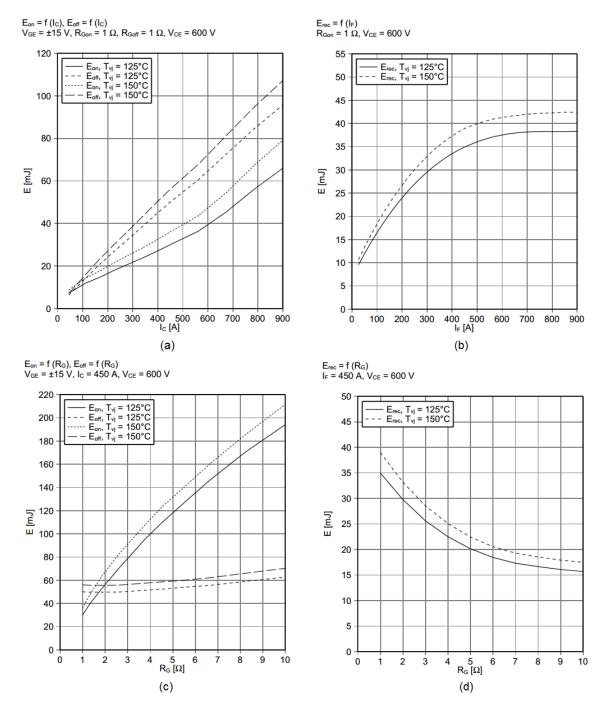

| 2.9  | Curvas do catálogo do módulo comercial trifásico FF450R12KE4 (Infineon)          | 20 |

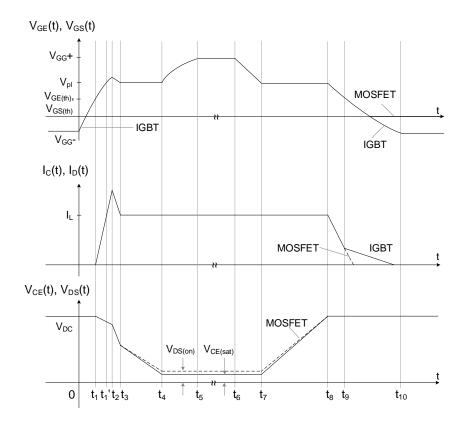

| 2.10 | Circuitos considerados nas análises do processo de chaveamento                   | 22 |

| 2.11 | Processo de chaveamento em MOSFETs e IGBTs                                       | 23 |

| 2.12 | Curvas do catálogo do módulo comercial trifásico FF450R12KE4 (Infineon)          | 28 |

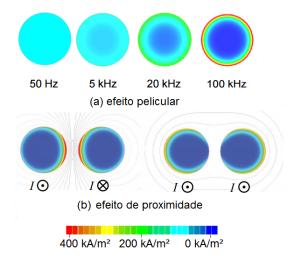

| 2.13 | Perfil das correntes ao longo da seção reta do condutor com os efeitos pelicular |    |

|      | e proximidade                                                                    | 30 |

| 2.14 | Circuitos térmicos equivalentes de regime permanente                             | 33 |

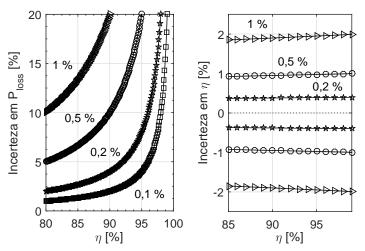

| 2.15 | Incertezas na medição de perdas e de rendimento, em função do rendimento do      |    |

|      | conversor, para wattímetros de várias classes de exatidão (indicadas sobre as    |    |

|      | curvas)                                                                          | 35 |

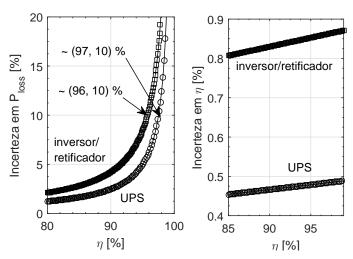

| 2.16 | Incertezas na medição de perdas e de rendimento, em função do rendimento do      |    |

|      | conversor, para os ensaios propostos na UPS hipotética de $7,2kW$ e frequência   |    |

|      | de chaveamento de $20kHz$                                                        | 36 |

| 2.17 | Arranjo típico dos conversores no método da oposição                             | 37 |

| 2.18 | Classificação dos calorímetros                                                   | 39 |

| 2.19 | Diagrama de um calorímetro direto, aberto e refrigerado a ar                     | 39 |

| 2.20 | Diagrama de um calorímetro direto, fechado e refrigerado à água                  | 41 |

| 2.21 | Diagrama de um calorímetro indireto balanceado                                   | 42 |

| 2.22 | Diagrama de um calorímetro indireto do tipo série                                | 43 |

| 3.1  | Topologia de inversor de dois níveis                                             | 45 |

| 3.2  | Tensões de saída de linha de um inversor de topologias de dois e de três níveis. | 46 |

| 3.3  | Topologias de inversores de três níveis                                          | 47 |

| 3.4  | Diagrama esquemático das UPSs de dupla conversão avaliadas                       | 50 |

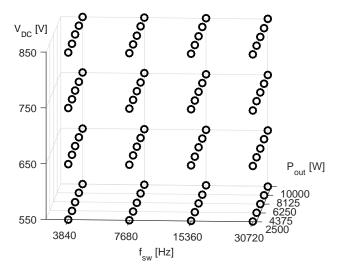

| 3.5  | Representação gráfica das UPSs simuladas (indicadas por círculos), com as        |    |

|      | respectivas especificações                                                       | 51 |

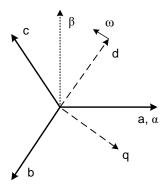

| 3.6  | Orientação adotada para os eixos de referência                                   | 52 |

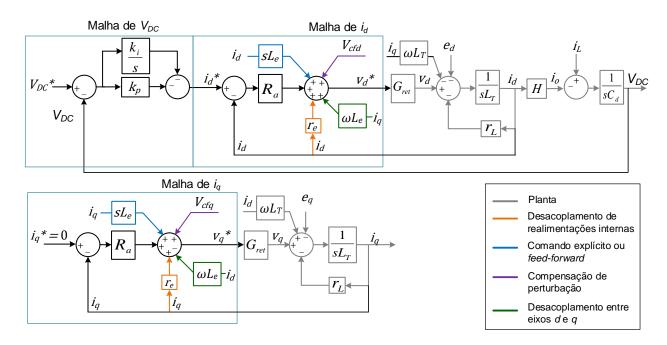

| 3.7  | Diagrama de controle do retificador trifásico                                             | 5 |

|------|-------------------------------------------------------------------------------------------|---|

| 3.8  | Diagrama de PLL implementado                                                              | 5 |

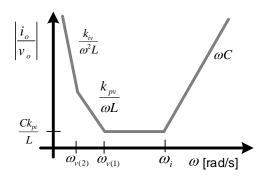

| 3.9  | Esboço das assíntotas das curvas de rigidez dinâmica.                                     | 5 |

| 3.10 | Resultados da simulação de um retificador trifásico com os parâmetros da                  |   |

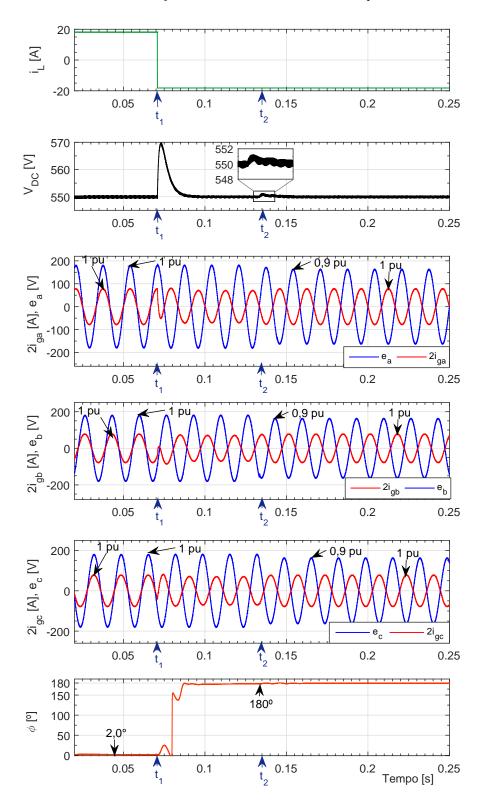

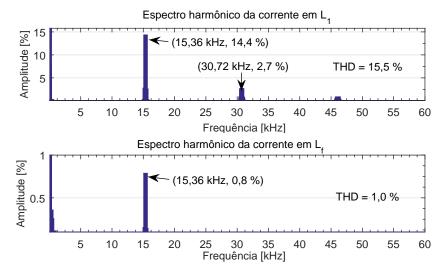

|      | Tabela 3.3                                                                                | 5 |

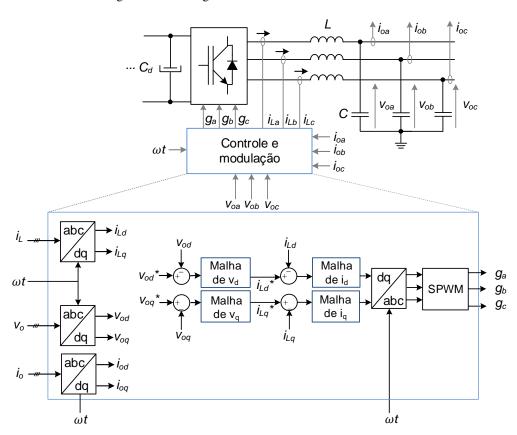

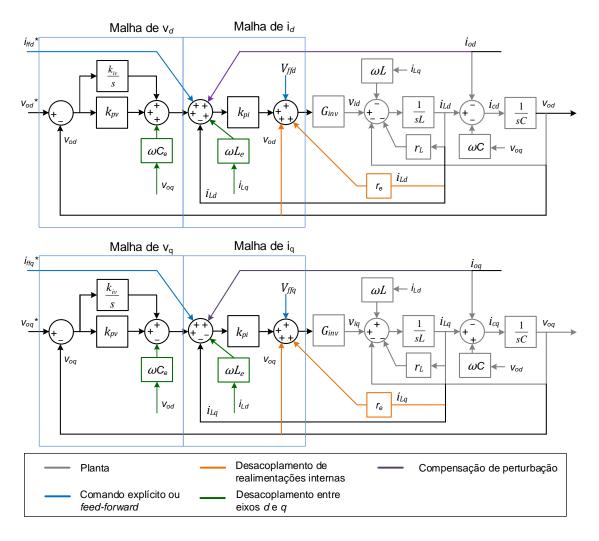

| 3.11 | Diagrama de controle do inversor trifásico                                                | 6 |

| 3.12 | Esboço das assíntotas da curva de rigidez dinâmica $ i_o/v_o $                            | 6 |

| 3.13 | Resultados da simulação de um inversor trifásico com os parâmetros da Tabela              |   |

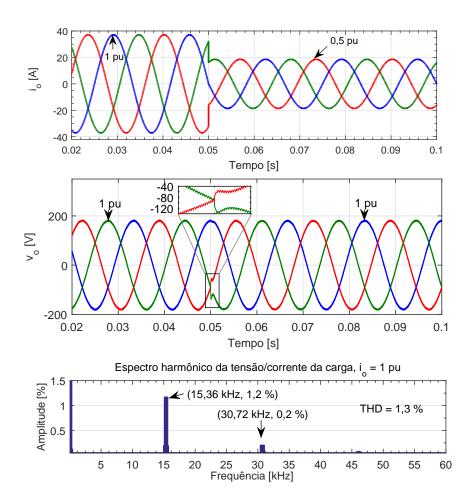

|      | 3.4                                                                                       | 6 |

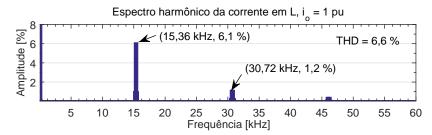

| 4.1  | Diagrama esquemático dos métodos online e offline de cálculos de perdas nos               |   |

|      | módulos semicondutores de potência                                                        | 7 |

| 4.2  | Fluxograma da ferramenta GetPoints                                                        | 7 |

| 4.3  | Algumas telas da ferramenta GetPoints, com algumas das etapas do fluxograma               |   |

|      | da Figura 4.2.                                                                            | 7 |

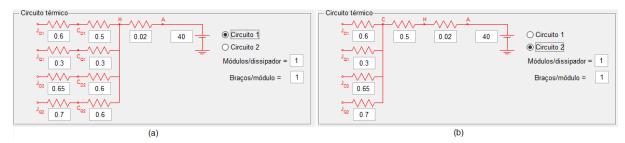

| 4.4  | Detalhe da seleção do tipo de circuito térmico de um conversor com topologia              |   |

|      | NPC2                                                                                      | 7 |

| 4.5  | Diagramas dos circuitos térmicos propostos com os elementos do pacote Foun-               |   |

|      | dation Library/Thermal, da biblioteca Simscape                                            | 7 |

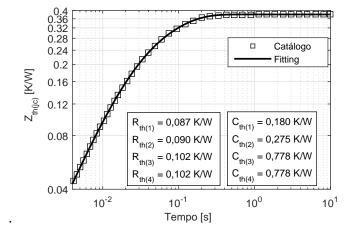

| 4.6  | Exemplo de ajuste dos parâmetros do circuito térmico de regime transitório                |   |

|      | do tipo $Foster$ , a partir da curva de impedância térmica transitória $Z_{th(jc)}$ do    |   |

|      | dispositivo semicondutor.                                                                 | 7 |

| 4.7  | Fluxograma da ferramenta PerdasOffline, que implementa o método de cálculo                |   |

|      | de perdas <i>offline</i>                                                                  | 8 |

| 4.8  | Telas da ferramenta <i>PerdasOffline</i> , em parte das fases do fluxograma da Figura     |   |

|      | 4.7                                                                                       | 8 |

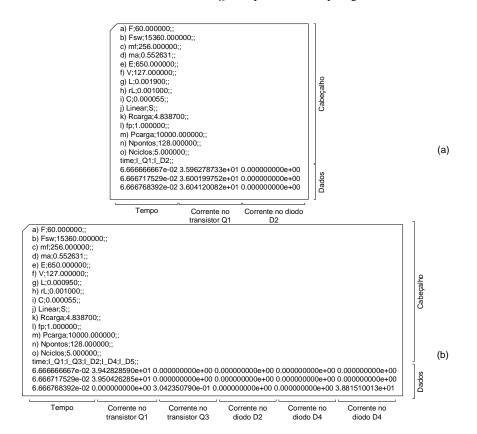

| 4.9  | Formato dos vetores de corrente que devem ser importados em arquivos ".txt"               |   |

|      | no programa <i>PerdasOffline</i> , para as três topologias                                | 8 |

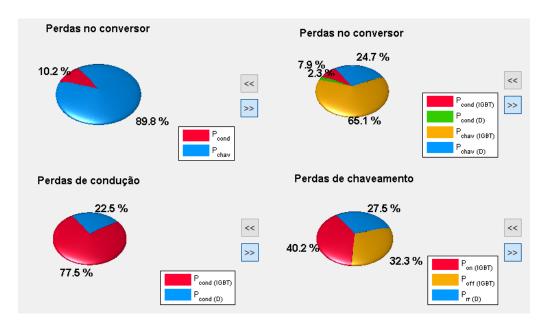

| 4.10 | Gráficos com as estatísticas de perdas nos conversores, exibidos na interface do          |   |

|      | PerdasOffline                                                                             | 8 |

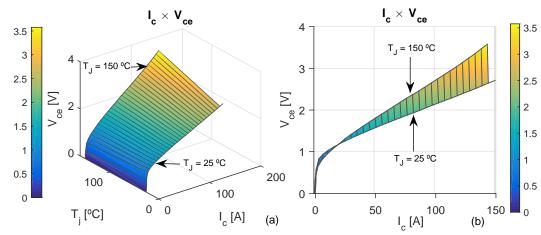

| 4.11 | Característica "tensão × corrente" do módulo FF75R12RT4                                   | 8 |

| 4.12 | Avaliação da técnica de interpolação via função 2-D Lookup Table para o módulo FF75R12RT4 | 8 |

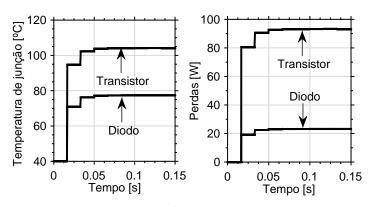

| 4.13 | Evolução das perdas e da temperatura de junção em um conversor arbitrário no              |   |

|      | método <i>online</i>                                                                      | 9 |

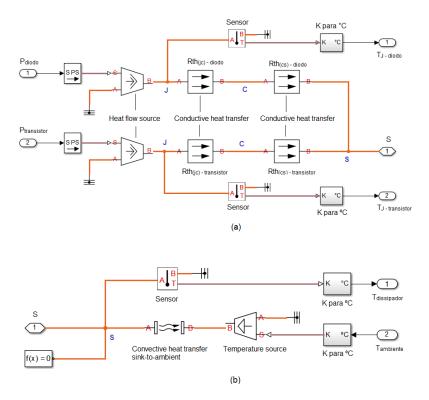

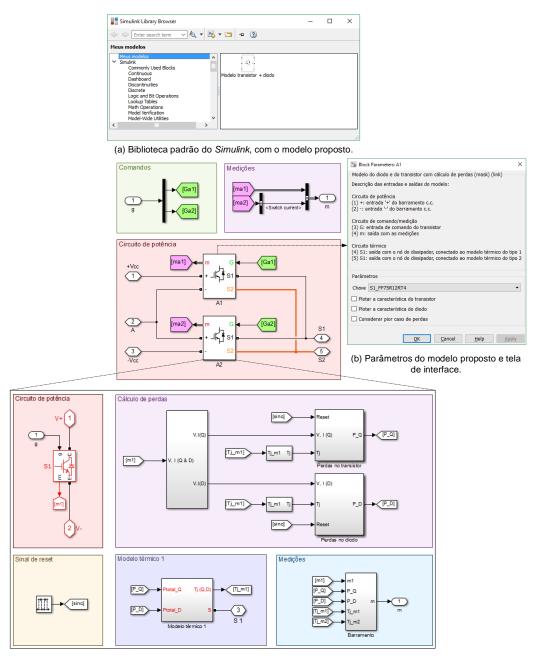

| 4.14 | Modelo do par "transistor + diodo em antiparalelo", encapsulado em biblioteca             |   |

|      | do Simulink, como parte do método online                                                  | 9 |

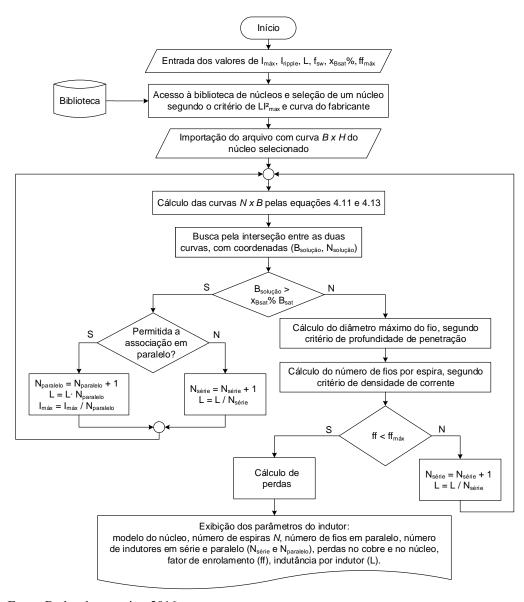

| 4.15 | Fluxograma com a sequência de procedimentos para o projeto dos indutores                  |   |

|      | dos filtros de entrada e de saída                                                         | 9 |

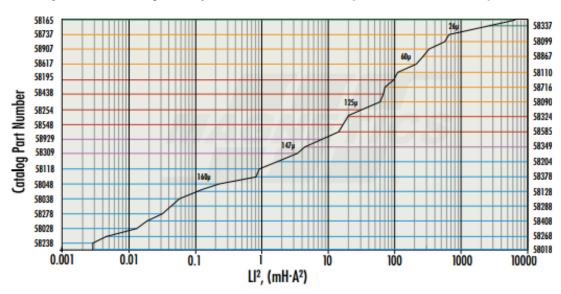

| 4.16 | Curva para seleção de núcleos da família High Flux do fabricante Magnetics                | 9 |

|      |                                                                                           |   |

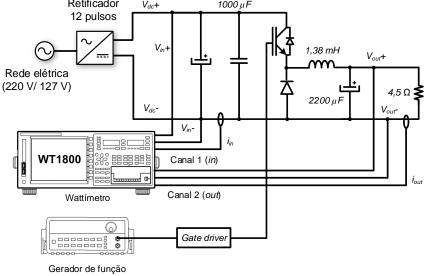

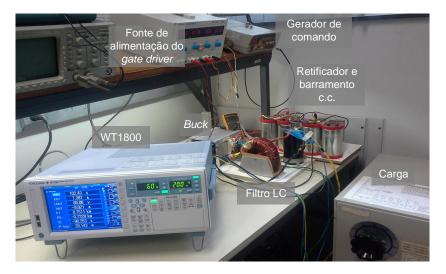

| 4.17 | Protótipo experimental desenvolvido para a medição de perdas via wattímetro.           | 96  |

|------|----------------------------------------------------------------------------------------|-----|

| 4.18 | Protótipo experimental desenvolvido para a medição de perdas via wattímetro.           | 97  |

| 4.19 | Diagrama esquemático do protótipo experimental desenvolvido para a medição             |     |

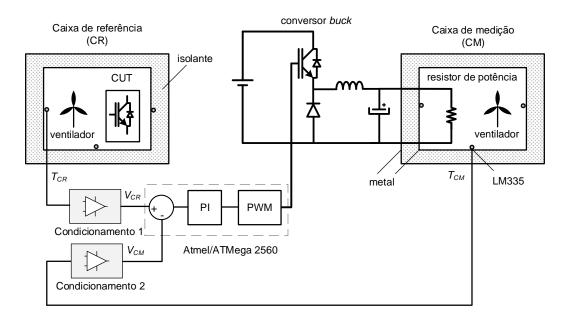

|      | de perdas via calorímetro indireto série                                               | 98  |

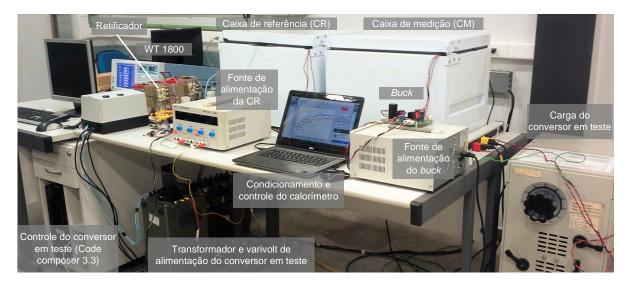

| 4.20 | Protótipo experimental desenvolvido para a medição de perdas                           | 99  |

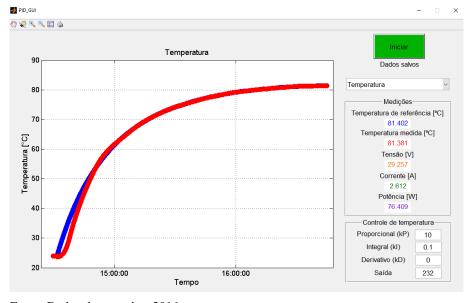

| 4.21 | Tela de interface gráfica com o usuário implementada para execução dos ensaios         |     |

|      | no calorímetro                                                                         | 103 |

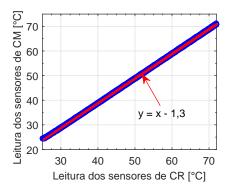

| 4.22 | Resultados da calibração por comparação das leituras de temperatura média              |     |

|      | dos dois conjuntos de sensores LM335, originalmente nas caixas CR e CM                 | 104 |

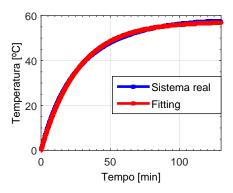

| 4.23 | Variação da temperatura em CR em resposta ao degrau de potência, obtida                |     |

|      | experimentalmente e ajuste pela função $f(t)=57(1-e^{-t/1594}).$                       | 105 |

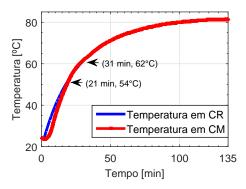

| 4.24 | Dinâmicas de aquecimento na condição em que os ganhos do controlador PI                |     |

|      | são atribuídos a $k_p=10$ e $k_i=0,1,\ldots$                                           | 106 |

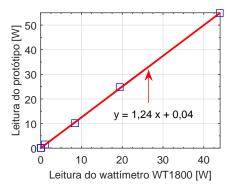

| 4.25 | Resultado da calibração em potência do protótipo                                       | 107 |

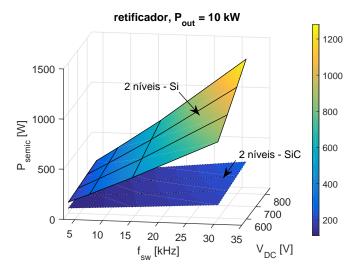

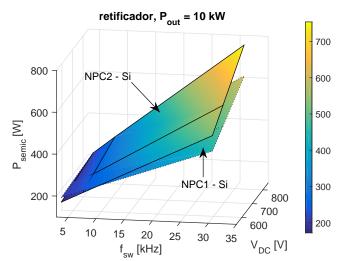

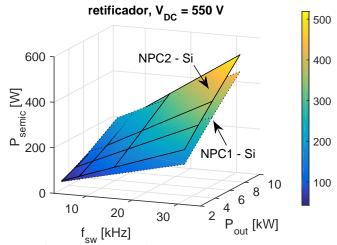

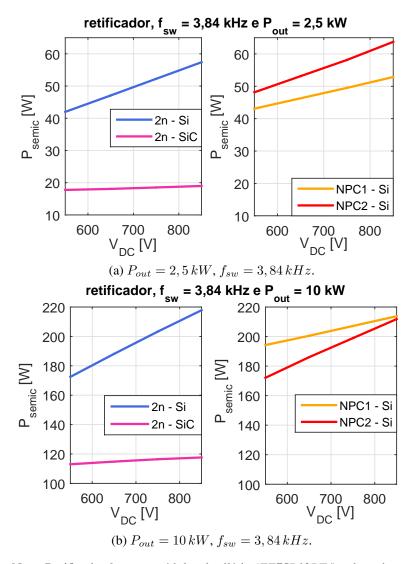

| 5.1  | Perdas nos semicondutores $P_{semic}$ do retificador trifásico em função da tensão     |     |

|      | do barramento $V_{DC}$ e da frequência de chaveamento $f_{sw}$ , para as UPSs com      |     |

|      | potência nominal $P_{out}$ de $10  kW$                                                 | 109 |

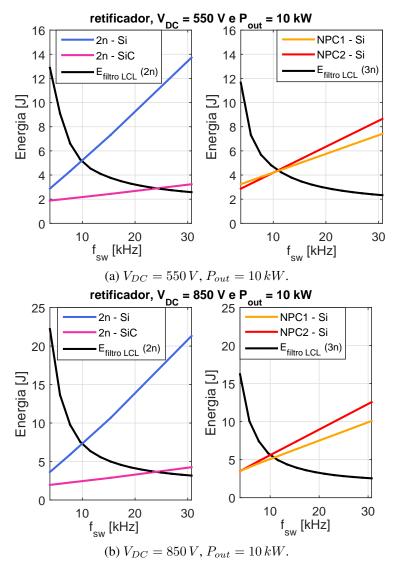

| 5.2  | Energia dissipada nos semicondutores do retificador trifásico e armazenada no          |     |

|      | filtro LCL de entrada em função da frequência de chaveamento $f_{sw}$ , para as        |     |

|      | UPSs de potência nominal $P_{out}$ de $10kW$ em topologias de dois níveis $(2n)$ e     |     |

|      | de três níveis $(3n)$                                                                  | 111 |

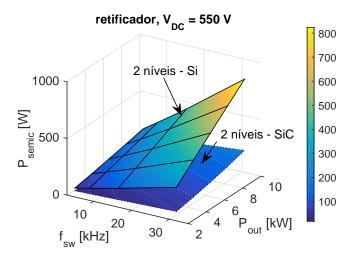

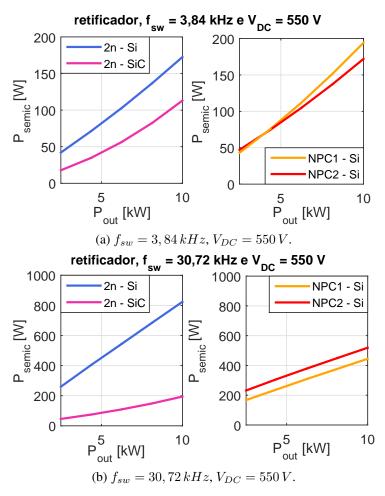

| 5.3  | Perdas nos semicondutores $P_{semic}$ do retificador trifásico em função da potência   |     |

|      | nominal $P_{out}$ e da frequência de chaveamento $f_{sw}$ , para as UPSs com tensão no |     |

|      | barramento c.c. $V_{DC}$ de $550 V$                                                    | 113 |

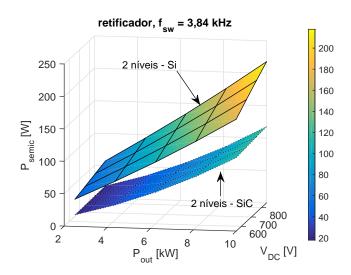

| 5.4  | Perdas nos semicondutores $P_{semic}$ do retificador trifásico em função da potência   |     |

|      | de saída $P_{out}$ , para as UPSs com tensão no barramento c.c. $V_{DC}$ de $550V$     | 114 |

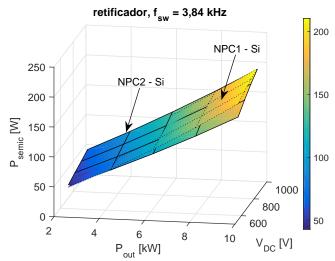

| 5.5  | Perdas nos semicondutores $P_{semic}$ do retificador trifásico em função da potência   |     |

|      | de saída $P_{out}$ e da tensão do barramento $V_{DC}$ , para as UPSs com frequência de |     |

|      | chaveamento $f_{sw}$ de $3,84  kHz$                                                    | 115 |

| 5.6  | Perdas nos semicondutores $P_{semic}$ do retificador trifásico em função da tensão     |     |

|      | do barramento $V_{DC}$ , para as UPSs com frequência de chaveamento $f_{sw}$ de        |     |

|      | 3,84kHz                                                                                | 116 |

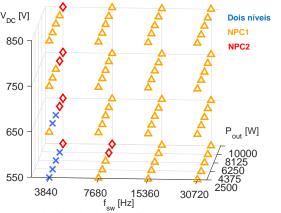

| 5.7  | Representação gráfica das UPSs simuladas, com a indicação das topologias               |     |

|      | com módulos de silício com menores perdas no estágio retificador                       | 117 |

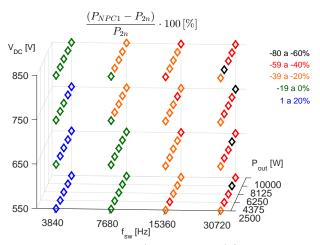

| 5.8  | Diferença percentual entre as perdas no retificador em topologias NPC1 e $2n$ ,        |     |

|      |                                                                                        | 119 |

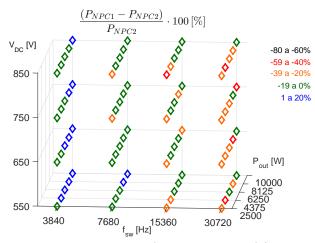

| 5.9  | Diferença percentual entre as perdas no retificador em topologias NPC1 e NPC2,         |     |

|      | com módulos à base de silício                                                          | 119 |

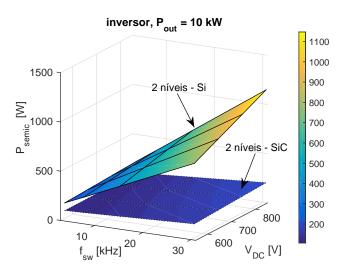

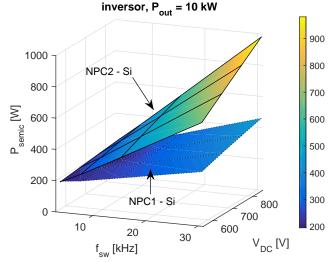

| 5.10 | Perdas nos semicondutores $P_{semic}$ do inversor trifásico em função da frequência de chaveamento $f_{sw}$ e da tensão de barramento $V_{DC}$ , para as UPSs com potência |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | de saída $P_{out}$ de $10  kW$                                                                                                                                             | 121 |

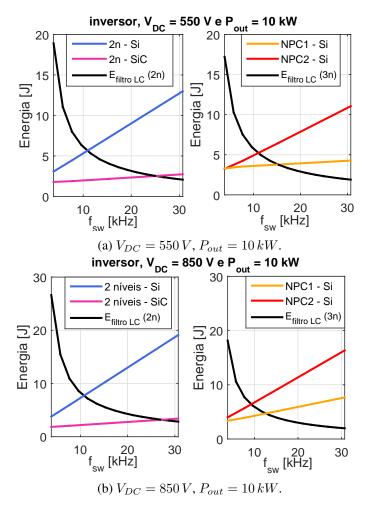

| 5.11 | Energia dissipada nos semicondutores do inversor trifásico e armazenada no                                                                                                 | 121 |

| J.11 | filtro LC de saída em função da frequência de chaveamento $f_{sw}$ , para as UPSs                                                                                          |     |

|      | com potência nominal de $10  kW$                                                                                                                                           | 122 |

| 5.12 | Comparação entre as energias armazenadas nos filtros das topologias de dois                                                                                                | 122 |

| J.12 | níveis $(E_{2n})$ e três níveis $(E_{3n})$                                                                                                                                 | 124 |

| 5.13 | Perdas nos semicondutores $P_{semic}$ do inversor trifásico em função da potência                                                                                          | 144 |

| J.13 | de saída $P_{out}$ e da tensão do barramento $V_{DC}$ , para as UPSs com frequência de                                                                                     |     |

|      | chaveamento $f_{sw}$ de 3, 84 $kHz$                                                                                                                                        | 125 |

| 5.14 | Perdas nos semicondutores $P_{semic}$ do inversor trifásico em função da tensão                                                                                            |     |

|      | do barramento c.c. $V_{DC}$ , para as UPSs com frequência de chaveamento $f_{sw}$ de                                                                                       |     |

|      | 3,84kHz                                                                                                                                                                    | 126 |

| 5.15 | Representação gráfica das UPSs simuladas, com a indicação das topologias                                                                                                   |     |

|      | com menores perdas no estágio inversor.                                                                                                                                    | 127 |

| 5.16 | Proporção, na operação como <i>retificador</i> , entre as perdas de chaveamento                                                                                            |     |

|      | no diodo (indicadas pela cor vermelha), de condução no diodo (amarelo), de                                                                                                 |     |

|      | chaveamento no transistor (azul) e de condução no transistor (verde)                                                                                                       | 129 |

| 5.17 | Proporção, na operação como <i>inversor</i> , entre as perdas de chaveamento no diodo                                                                                      |     |

|      | (indicadas pela cor vermelha), de condução no diodo (amarelo), de chaveamento                                                                                              |     |

|      | no transistor (azul) e de condução no transistor (verde).                                                                                                                  | 129 |

| 5.18 | Comparação entre as perdas nas topologias NPC1 e $2n$ na operação como                                                                                                     |     |

|      | inversor, com módulos à base de silício                                                                                                                                    | 130 |

| 5.19 | Comparação entre as perdas nas topologias NPC1 e NPC2 na operação como                                                                                                     |     |

|      | inversor, com módulos à base de silício                                                                                                                                    | 130 |

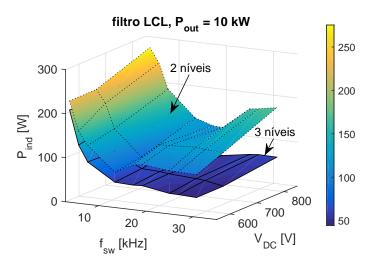

| 5.20 | Perdas totais $P_{ind}$ no indutor do filtro LCL de entrada da UPS em função da                                                                                            |     |

|      | frequência de chaveamento $f_{sw}$ e da tensão de barramento $V_{DC}$ , para topologias                                                                                    |     |

|      | de dois níveis e de três níveis, para a UPS com potência nominal de $10kW.$                                                                                                | 132 |

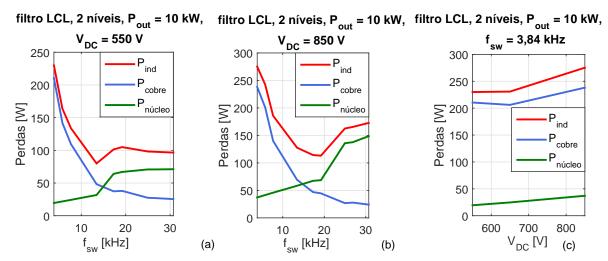

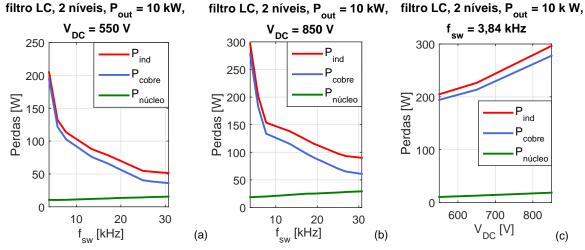

| 5.21 | Perdas no enrolamento $P_{cobre}$ , no núcleo $P_{nucleo}$ e totais $P_{ind}$ para os indutores                                                                            |     |

|      | do filtro LCL de entrada de <i>retificadores</i> em topologia de <i>dois</i> níveis                                                                                        | 132 |

| 5.22 | Perdas no enrolamento $P_{cobre}$ , no núcleo $P_{nucleo}$ e totais $P_{ind}$ para os indutores                                                                            |     |

|      | do filtro LCL de entrada de <i>retificadores</i> em topologia de <i>três</i> níveis                                                                                        | 133 |

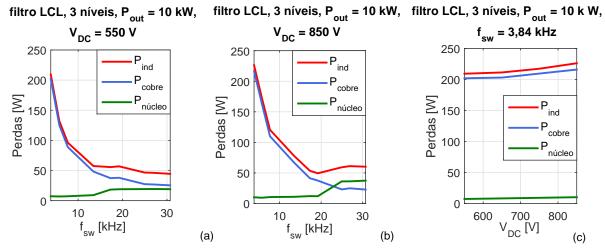

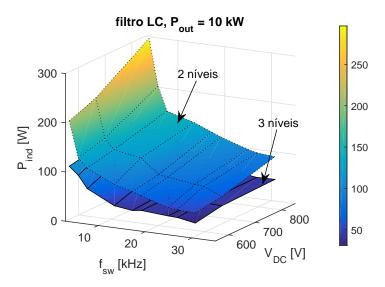

| 5.23 | Perdas no indutor $P_{ind}$ do filtro LC de saída da UPS em função da frequência                                                                                           |     |

|      | de chaveamento $f_{sw}$ e da tensão de barramento $V_{DC}$ , para topologias de dois                                                                                       |     |

|      | níveis e de três níveis, para a UPS com potência nominal de $10kW.$                                                                                                        | 134 |

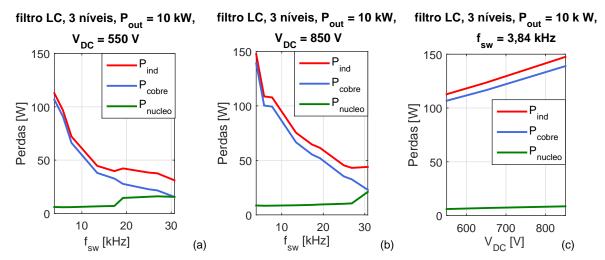

| 5.24 | Perdas no enrolamento $P_{cobre}$ , no núcleo $P_{nucleo}$ e totais $P_{ind}$ para os indutores                                                                            |     |

|      | do filtro LC de saída de <i>inversores</i> em topologia de <i>dois</i> níveis                                                                                              | 135 |

|      |                                                                                                                                                                            |     |

| 5.25        | Perdas no enrolamento $P_{cobre}$ , no núcleo $P_{nucleo}$ e totais $P_{ind}$ para os indutores |     |

|-------------|-------------------------------------------------------------------------------------------------|-----|

|             | do filtro LC de saída de <i>inversores</i> em topologia de <i>três</i> níveis                   | 135 |

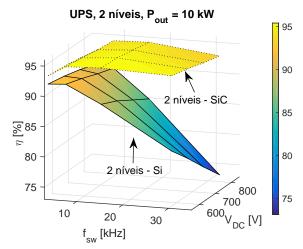

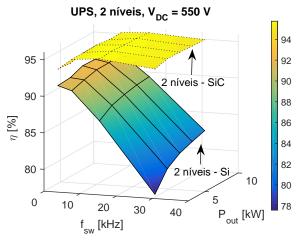

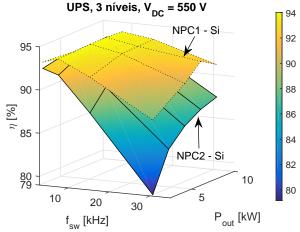

| 5.26        | Rendimento global da UPS de dupla conversão em função da frequência de                          |     |

|             | chaveamento $f_{sw}$ e da tensão do barramento c.c. $V_{DC}$ , para as UPSs com                 |     |

|             | potência nominal $P_{out}$ de $10  kW$                                                          | 138 |

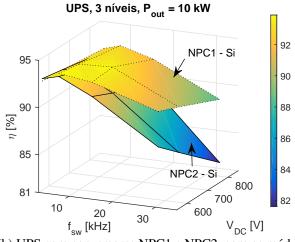

| 5.27        | Rendimento global da UPS de dupla conversão em função da frequência de                          |     |

|             | chaveamento $f_{sw}$ e da potência nominal $P_{out}$ , para as UPSs com tensão de               |     |

|             | barramento $V_{DC}$ de $550 V$                                                                  | 140 |

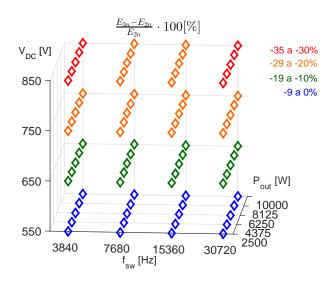

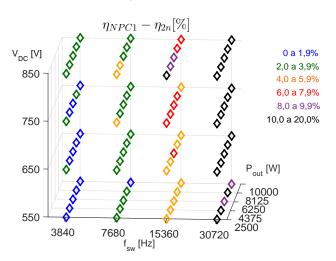

| 5.28        | Comparação entre o rendimento global da UPS de dupla conversão nas topolo-                      |     |

|             | gias NPC1 e dois níveis, com módulos à base de silício                                          | 141 |

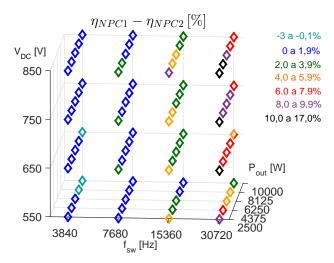

| 5.29        | Comparação entre o rendimento global da UPS de dupla conversão nas topolo-                      |     |

|             | gias NPC1 e NPC2, com módulos à base de silício                                                 | 142 |

| 5.30        | Comparação entre o rendimento global da UPS de dupla conversão com conver-                      |     |

|             | sores de dois níveis e NPC1 com módulos de SiC e de silício, respectivamente.                   | 143 |

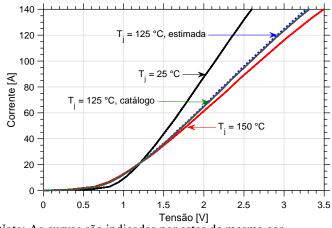

| 5.31        | Características $I \times V$ informadas no catálogo do módulo FF75R12RT4                        | 150 |

| 5.32        | Rendimento global $\eta$ do conversor <i>buck</i> calculado e medido via wattímetro,            |     |

|             | para várias potências de carga $P_{out}$                                                        | 151 |

| 5.33        | Resultados do ensaio 1, com descrição dada na Tabela 5.9                                        | 155 |

| 5.34        | Resultados do ensaio 2, com descrição dada na Tabela 5.9                                        | 156 |

| 5.35        | Resultados do ensaio 3, com descrição dada na Tabela 5.9                                        | 156 |

| 5.36        | Resultados do ensaio 4, com descrição dada na Tabela 5.9                                        | 157 |

| 5.37        | Resultados do ensaio 5, com descrição dada na Tabela 5.9                                        | 158 |

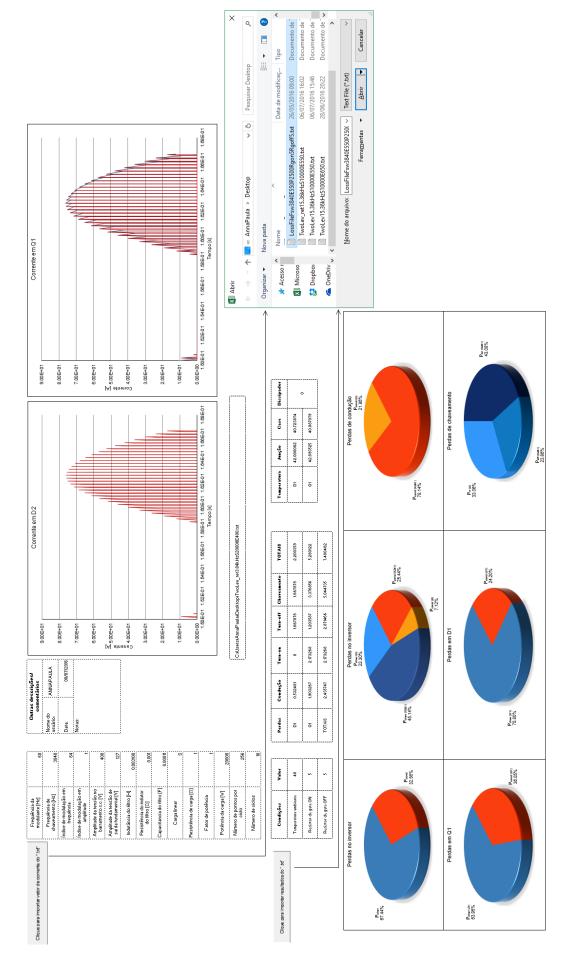

| <b>A.</b> 1 | Formatação dos relatórios gerados pelo programa PerdasOffline                                   | 169 |

| A.2         | Planilhas em Excel, programadas em VBA, para documentação dos resultados                        |     |

|             | de simulação de conversores em topologia de dois níveis                                         | 171 |

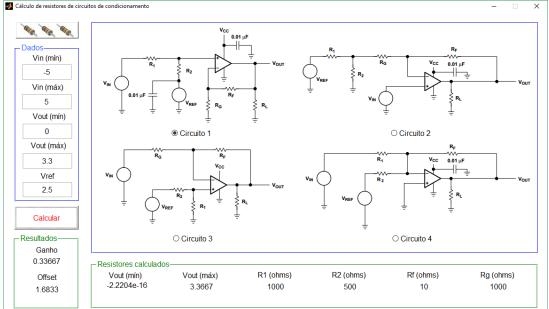

| B.1         | Interface gráfica do programa desenvolvido para automatizar o dimensiona-                       |     |

|             | mento dos resistores do circuito de condicionamento.                                            | 172 |

|             |                                                                                                 |     |

## LISTA DE TABELAS

| 35<br>49<br>49 |

|----------------|

| 49<br>49       |

| 49             |

| 49             |

|                |

|                |

| <i></i>        |

|                |

| 57             |

|                |

| 63             |

| 85             |

|                |

| 118            |

|                |

| 123            |

|                |

| 128            |

|                |

| 137            |

|                |

| 139            |

|                |

|                |

| 145            |

|                |

|                |

| 147            |

| 149            |

| 152            |

| 154            |

|                |

## LISTA DE ABREVIATURAS E SIGLAS

ABNT Associação Brasileira de Normas Técnicas

CM Caixa de Medição

CR Caixa de Referência

CUT Converter Under Test

IEC International Electrotechnical Commission

IGBT Insulated Gate Bipolar Transistor

iGSE improved Generalized Steinmetz Equation

MOSFET Metal Oxide Semiconductor Field Effect

NPC Neutral-Point Clamped

PI Proporcional-Integral

PLL Phase Locked Loop

PWM Pulse-Width Modulation

Si Silício

SiC Carbeto de silício

UPSs Uninterruptible Power Supplies

VBA Visual Basic for Applications

2*n* Dois níveis

*3n* Três níveis

## LISTA DE SÍMBOLOS

$\alpha$  Coeficiente de temperatura

$\eta$  Rendimento

$\sigma$  Desvio padrão

μ Permeabilidade

$\rho$  Resistividade

δ Profundidade de penetração

f Frequência

V Volume

B Densidade de fluxo

$P_{loss}$  Perdas

$P_{in}$  Potência de entrada

$P_{out}$  Potência nominal

$f_{sw}$  Frequência de chaveamento

$V_{DC}$  Tensão do barramento c.c.

$T_i$  Temperatura de junção

$v_{sw}$  Tensão sobre a chave

$i_{sw}$  Corrente na chave

$r_{sw}$  Resistência da chave

$R_q$  Resistor de gate

$v_q$  Tensão sobre o transistor

$i_q$  Corrente no transistor

$v_d$  Tensão sobre o diodo

$i_d$  Corrente no diodo

$V_{CE}$  Tensão coletor-emissor

$I_C$  Corrente de coletor

$V_{GE}$  Tensão gate-emissor

$V_{GE(th)}$  Tensão gate-emissor de limiar

$V_{DS}$  Tensão dreno-fonte

$I_D$  Corrente de dreno

$V_{GS}$  Tensão gate-fonte

$V_{GS(th)}$  Tensão gate-fonte de limiar

$T_s$  Passo de simulação

$P_{cond(Q)}$  Perdas de condução no transistor

$P_{cond(D)}$  Perdas de condução no diodo

$R_G$  Resistência total de gate

$R_{q(on)}$  Resistência de *gate* no processo de *turn-on*

$R_{g(off)}$  Resistência de gate no processo de turn-off

$V_{GG}$  Tensão de disparo no gate

$E_{on(Q)}$  Energia dissipada no processo de turn-on do transistor

$E_{off(Q)}$  Energia dissipada no processo de turn-off do transistor

$E_{rr}$  Energia dissipada no processo de recuperação reversa do diodo

$P_{on(Q)}$  Perdas no processo de *turn-on* do transistor

$P_{off(Q)}$  Perdas no processo de *turn-off* do transistor

$P_{rr}$  Perdas no processo de recuperação reversa do diodo

$k_{Vdc}$  Fator de correção da tensão do barramento c.c.

$k_{Rq}$  Fator de correção do resistor de gate

$R_{cc'-ee'}$  Resistência série parasita

Número de espiras

$\bar{P}_{nucleo}$  Perdas médias no núcleo

$P_{cobre}$  Perdas no cobre

$P_{ind}$  Perdas totais no indutor

$S_{total}$  Área da superfície

$E_{filtro}$  Energia armazenada nos filtros

$E_{dissip}$  Energia dissipada nos semicondutores

$E_{2n}$  Energia armazenada nos filtros do conversor em topologia de dois níveis

$E_{3n}$  Energia armazenada nos filtros do conversor em topologia de três níveis

$P_{2n}$  Perdas do conversor em topologia de dois níveis

$P_{NPC1}$  Perdas do conversor em topologia NPC1

$P_{NPC2}$  Perdas do conversor em topologia NPC2

$\eta_{2n}$  Rendimento global do conversor em topologia de dois níveis

$\eta_{NPC1}$  Rendimento global do conversor em topologia NPC1

$\eta_{NPC2}$  Rendimento global do conversor em topologia NPC2

$P_{CR}$  Potência do resistor da caixa de referência

$P_{CM}$  Potência do resistor da caixa de medição

$T_{CR}$  Temperatura interna da caixa de referência

$T_{CM}$  Temperatura interna da caixa de medição

# **SUMÁRIO**

| 1       | INTRODUÇÃO                                         | 3  |

|---------|----------------------------------------------------|----|

| 2       | REVISÃO BIBLIOGRÁFICA                              | 8  |

| 2.1     | UPS: definição e classificação                     | 8  |

| 2.1.1   | UPSs rotativas                                     | 10 |

| 2.1.2   | UPSs híbridas                                      | 11 |

| 2.1.3   | UPSs estáticas                                     | 12 |

| 2.1.3.1 | UPS estáticas passivas ou offline                  | 13 |

| 2.1.3.2 | UPS estáticas line-interactive                     | 15 |

| 2.1.3.3 | UPS estáticas de dupla conversão ou online         | 16 |

| 2.2     | Perdas em conversores e modelos térmicos           | 18 |

| 2.2.1   | Perdas nos semicondutores                          | 18 |

| 2.2.1.1 | Perdas de condução                                 | 19 |

| 2.2.1.2 | Perdas de chaveamento                              | 21 |

| 2.2.2   | Perdas nos indutores                               | 29 |

| 2.2.3   | Modelos térmicos de regime permanente              | 31 |

| 2.3     | Métodos de medição de perdas                       | 33 |

| 2.3.1   | Medição elétrica                                   | 34 |

| 2.3.2   | Medição via calorímetro                            | 38 |

| 2.3.2.1 | Calorímetros diretos, abertos e refrigerados a ar  | 39 |

| 2.3.2.2 | Calorímetros diretos, fechados refrigerados à água | 40 |

| 2.3.2.3 | Calorímetros indiretos balanceados                 | 42 |

| 2.3.2.4 | Calorímetros indiretos do tipo série               | 43 |

| 2.4     | Conclusões do capítulo                             | 44 |

| 3       | MODELAGEM E SIMULAÇÃO DA UPS DE DUPLA CONVERSÃO .  | 45 |

| 3.1     | Circuitos de potência em estudo                    | 45 |

| 3.2     | Controle dos estágios da UPS                       | 51 |

| 3.2.1   | Controle do retificador                            | 52 |

| 3.2.2   | Controle do inversor                               | 59 |

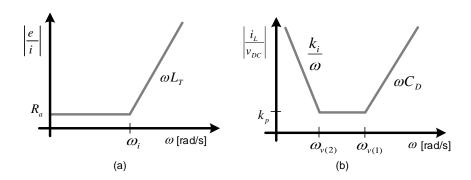

| 3.3     | Dimensionamento dos filtros de entrada e de saída  | 64 |

| 3.3.1   | Dimensionamento do filtro LCL                      | 64 |

| 3.3.2   | Dimensionamento do filtro LC                       | 68 |

| 3.4     | Conclusões do capítulo                             | 68 |

| 4       | CÁLCULO E MEDIÇÃO DE PERDAS EM CONVERSORES         | 70 |

| 4.1     | Ferramentas desenvolvidas para cálculo de perdas                               | 70  |  |  |

|---------|--------------------------------------------------------------------------------|-----|--|--|

| 4.1.1   | Rotinas para cálculo de perdas nos semicondutores                              | 71  |  |  |

| 4.1.1.1 | Caracterização teórica do componente e modelos térmicos                        | 73  |  |  |

| 4.1.1.2 | Método offline                                                                 | 79  |  |  |

| 4.1.1.3 | Método online                                                                  | 87  |  |  |

| 4.1.2   | Rotinas para o cálculo de perdas nos indutores                                 | 91  |  |  |

| 4.2     | Protótipos experimentais para medição de perdas                                | 96  |  |  |

| 4.2.1   | Protótipo para medição via wattímetro                                          | 96  |  |  |

| 4.2.2   | Protótipo de calorímetro indireto série                                        | 97  |  |  |

| 4.2.2.1 | Projeto mecânico do protótipo                                                  | 99  |  |  |

| 4.2.2.2 | Seleção dos sensores e dimensionamento dos componentes do circuito de condici- |     |  |  |

|         | onamento                                                                       | 100 |  |  |

| 4.2.2.3 | Seleção do microcontrolador e da interface com o usuário                       | 102 |  |  |

| 4.2.2.4 | Calibração dos sensores de temperatura por comparação                          | 103 |  |  |

| 4.2.2.5 | Projeto do controlador de temperatura                                          | 105 |  |  |

| 4.2.2.6 | Calibração de potência                                                         | 106 |  |  |

| 4.3     | Conclusões do capítulo                                                         | 107 |  |  |

| 5       | RESULTADOS                                                                     | 108 |  |  |

| 5.1     | Resultados de simulação                                                        | 108 |  |  |

| 5.1.1   | Comparação das perdas no estágio retificador                                   | 108 |  |  |

| 5.1.2   | Comparação das perdas no estágio inversor                                      | 120 |  |  |

| 5.1.3   | Perdas nos indutores dos filtros de entrada e de saída                         | 131 |  |  |

| 5.1.4   | Comparação do rendimento global da UPS                                         | 138 |  |  |

| 5.1.5   | Viabilidade de módulos de SiC em UPS                                           |     |  |  |

| 5.1.6   | Comparação entre os métodos online e offline                                   | 148 |  |  |

| 5.2     | Resultados experimentais                                                       | 150 |  |  |

| 5.2.1   | Resultados de medições com wattímetro                                          | 150 |  |  |

| 5.2.2   | Resultados preliminares no protótipo de calorímetro                            | 152 |  |  |

| 5.3     | Conclusões do capítulo                                                         | 158 |  |  |

| 6       | CONCLUSÕES E PROPOSTAS DE CONTINUIDADE                                         | 160 |  |  |

|         | REFERÊNCIAS                                                                    | 163 |  |  |

|         | APÊNDICES                                                                      | 168 |  |  |

|         | APÊNDICE A – FERRAMENTA EM <i>EXCEL</i> PARA GERAÇÃO DE RELATÓRIOS             | 169 |  |  |

| APÊNDICE B – PROGRAMA PARA CÁLCULO DOS RESISTORES |     |

|---------------------------------------------------|-----|

| DO CIRCUITO DE CONDICIONAMENTO                    | 172 |

## 1 INTRODUÇÃO

Os Sistemas de Energia Ininterrupta (SEI), referidos na literatura pelo acrônimo em inglês UPSs (*Uninterruptible Power Supplies*) e popularmente pelo termo *no-breaks*, são equipamentos que asseguram o suprimento de energia elétrica com altos níveis de confiabilidade, disponibilidade e de qualidade. Estes equipamentos são usuais em aplicações de missão crítica, em que a interrupção ou os distúrbios no fornecimento de energia podem levar a perdas financeiras e/ou sociais, como *datacenters*, hospitais, sistemas de telecomunicação e de tecnologia da informação (TI), controladores de processos industriais, entre outros. Nestas aplicações, prefere-se o uso de UPSs estáticas do tipo dupla conversão ou *online*, que se mantêm continuamente conectadas em série com a carga crítica, em regime normal de operação (TON; FORTENBURY, 2005). Deste modo, estas UPSs previnem os problemas associados não só a interrupções no fornecimento, como também a elevações/afundamentos temporários ou momentâneos de tensão, a variações de frequência, surtos, ruídos e distorções harmônicas (GUERRERO; VICUNA; UCEDA, 2007).

Em geral, as UPSs integram estágios conversores que invariavelmente introduzem perdas e, assim, consomem energia e limitam o rendimento do sistema completo. Por exemplo, segundo pesquisas financiadas pela Comissão de Energia do Estado da Califórnia (*California Energy Commission*), em 2005, o consumo de energia associado às perdas nos estágios de conversão somente de UPSs dos *datacenters*/polos de TI da Califórnia era de aproximadamente 1 *TWh* anuais. Sendo assim, estas perdas oneravam cerca de 100 milhões de dólares por ano, considerando as tarifas de energia praticadas naquele ano (TON; FORTENBURY, 2005). Ainda segundo este estudo, como o estado da Califórnia concentra aproximadamente 15 % dos *datacenters* dos EUA, os custos relativos a este consumo de energia das UPSs em *datacenters*, em todo o país, poderiam atingir quase 700 milhões de dólares anuais (ou 7, 1 *TWh* por ano). Estudos anteriores, financiados pelo Departamento de Energia dos EUA, estimavam aquele consumo de energia total de UPSs em todo o país em 5,8 *TWh*, no ano de 2002, com base em dados típicos de rendimento destes equipamentos (ROTH; GOLDSTEIN; KLEINMAN, 2004). Somente as UPSs *online*, preferidas nas aplicações de missão crítica, consumiam 3,8 *TWh* daquele montante.

Como resultado destas pesquisas, o *Lawrence Berkeley National Lab* (LBNL), instituição de pesquisa financiada pelo Departamento de Energia dos EUA, passou a considerar o aumento do rendimento das UPSs de *datacenters* como uma das ações para reduzir o consumo de energia no país (TON; FORTENBURY, 2005). Por outro lado, como também pontuam os estudos do LBNL, o uso de UPSs com maior rendimento promove ainda a redução dos custos e do consumo de energia dos sistemas de refrigeração externos (não computados naquelas estatísticas). Assim, o investimento total para a aquisição e operação do equipamento poderia ser substancialmente menor com o aumento da eficiência das UPSs. Outro ganho associado ao uso de UPSs mais

eficientes, não assinalados naquela pesquisa, decorre ainda da redução da magnitude e do volume dos componentes passivos dos filtros de saída e de entrada, na medida em que os conversores permitissem a operação em frequências de chaveamento maiores. Como resultado, o custo, o volume e o peso do equipamento também poderiam se tornar menores.

Neste contexto, há, pois, um esforço constante em elevar o rendimento das UPSs. Ademais, por força de restrições comerciais (*e.g.*, para maior competitividade do produto no mercado), as UPSs devem atender a critérios mínimos de rendimento. Como alternativas para o aumento da eficiência destes equipamentos, figuram-se, por exemplo: (*i*) alterações nas topologias dos conversores, já que o desempenho de cada topologia varia com as condições de operação (KEREKES et al., 2009); (*ii*) o uso de novos materiais e tecnologias de dispositivos semicondutores (*i.e.*, de novas famílias de módulos de potência ou de dispositivos baseados em semicondutores de banda larga, como o carbeto de silício) (MCBRYDE et al., 2010); (*iii*) o emprego de distintas técnicas de modulação (KOLAR; ERTL; ZACH, 1991); (*iv*) a especificação de núcleos e enrolamentos com menores perdas no projeto dos componentes dos filtros passivos (MAGNETICS, 2006) ou (*v*) a modularização das UPSs, para excursionar o ponto de operação das unidades individuais para a região de operação nominal, com maior rendimento (LBNL, 2012).

Assim, na fase de projeto da UPS, o fabricante deve ponderar os ganhos de cada uma daquelas alternativas quanto aos custos, rendimento, volume, complexidade, ruído, confiabilidade, entre outros. A avaliação correta destes ganhos, via modelos teóricos, pode reduzir o tempo de projeto das UPSs, por dispensar a necessidade de construção de vários protótipos para fins de comparação experimental de cada alternativa. Em especial, o cálculo correto da potência dissipada nos conversores não só orienta a classificação de várias abordagens quanto ao rendimento, como também permite a especificação dos dispositivos semicondutores e o dimensionamento apropriado dos sistemas de refrigeração da UPS. Adicionalmente, o cálculo de perdas subsidia ainda as análises de confiabilidade do conversor (MOROZUMI et al., 2003), em razão da correlação entre a probabilidade de falha e a variação na temperatura de junção dos semicondutores (que resulta das perdas e dos modelos térmicos). Cabe salientar aqui, de modo mais genérico, que as ferramentas de avaliação teórica das perdas servem ao projeto de *qualquer* conversor estático.

Por outro lado, o fabricante deve ainda caracterizar as UPSs produzidas (*e.g.*, quanto ao rendimento), como parte das análises que antecedem a introdução destes equipamentos no mercado. Para avaliar o rendimento, em particular, submete-se a UPS a um ensaio de medição de perdas. A metodologia deste ensaio deve ser definida com base na exatidão pretendida para a medição e nas restrições dos sensores disponíveis (*e.g.*, exatidão, resolução e banda de passagem finitas). Em geral, duas técnicas de medição de perdas são mais usuais na literatura. A primeira delas, mais simples e menos exata, deriva da medição das potências de entrada e de saída da UPS e da subtração destas leituras (XIAO; CHEN; ODENDAAL, 2007). Em razão da necessidade de sincronização das leituras de potência de entrada e de saída, bem como de tensão e corrente,

deve-se optar pelo uso de wattímetros. Todavia, estes wattímetros devem exibir larga banda de passagem e alta resolução na conversão A/D e ainda prover a sincronização exata das medições, para que as tensões/correntes pulsadas, típicas dos conversores de UPS, sejam corretamente medidas (STAFINIAK; KOSOBUDZKI, 2009). Ademais, como o rendimento individual destes conversores é elevado, os wattímetros em uso devem prover leituras de potência com incertezas menores do que as perdas (XIAO; CHEN; ODENDAAL, 2007). Isso, em geral, inviabiliza a medição acurada da potência dissipada em cada conversor com os wattímetros disponíveis no mercado (FUCHS et al., 2013). A segunda técnica de medição de perdas se mostra mais exata e se baseia na transferência do calor liberado pelo conversor para um fluido, via processos de convecção, radiação ou condução, em um sistema referido por "calorímetro" na literatura (CAO et al., 2010). A variação de temperatura deste fluido, com propriedades bem caracterizadas, quantifica indiretamente a potência dissipada pela amostra. Deste modo, a exatidão da medição de perdas independe das formas de onda de tensão e de corrente do equipamento ou da sincronização das leituras (KOSONEN et al., 2013). Contudo, em virtude da complexidade da construção das variações mais típicas de calorímetro, a medição por esta técnica pode se revelar inviável.

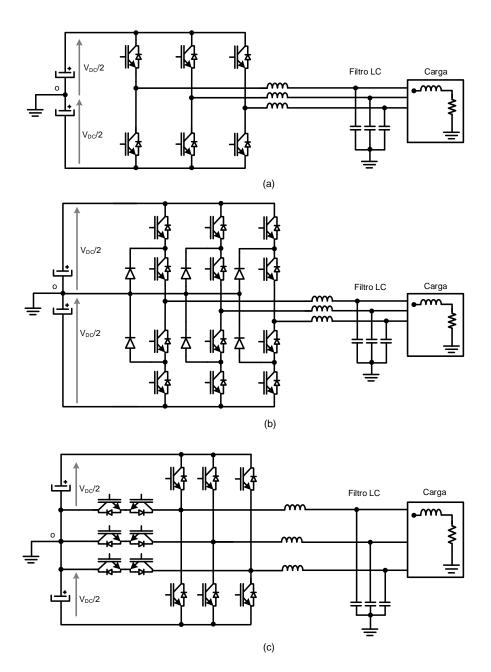

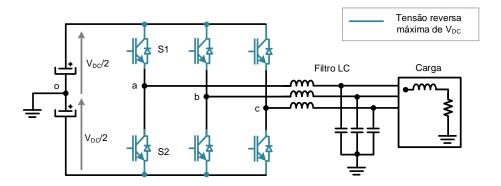

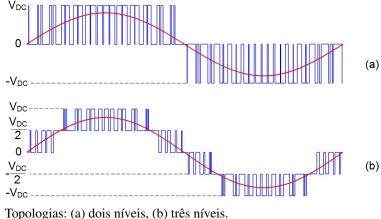

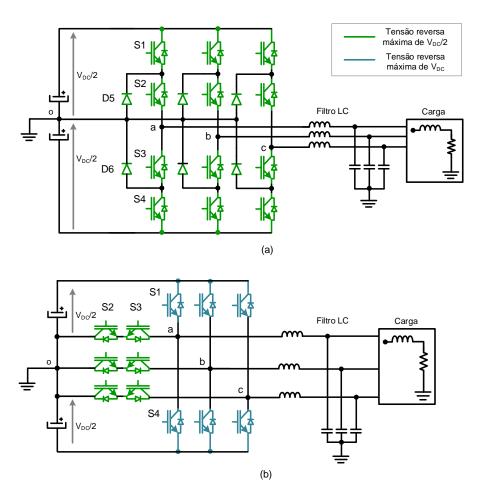

Neste contexto, este trabalho objetiva avaliar o rendimento de UPSs de dupla conversão em topologias trifásicas usuais nestas UPSs, a saber, a de dois níveis e as com neutro grampeado (*Neutral-Point Clamped*), denotadas neste texto por "NPC1" e "NPC2". Estas topologias constam na Figura 1.1. Em particular, pretende-se:

- (i) desenvolver ferramentas para estimar as perdas nos semicondutores e nos indutores e as temperaturas de junção e encapsulamento do dispositivo, bem como do dissipador, com base em dados dos catálogos dos módulos de potência;

- (ii) comparar o rendimento de módulos comerciais de carbeto de silício (SiC), em topologia de dois níveis, com o de módulos de silício, nas três topologias avaliadas;

- (iii) propor um calorímetro simples e de baixo custo, do tipo *indireto série*, para medição de perdas;

- (iv) validar experimentalmente o sistema proposto.

Para tanto, procede-se à revisão bibliográfica sobre as técnicas reportadas na literatura para cálculo e medição de perdas. Para estimar as perdas nos conversores, prefere-se o uso de simulações temporais, em alternativa ao cálculo analítico proposto por Schweizer, Friedli e Kolar (2010), para que, por exemplo, os efeitos de cargas não-lineares – tipo de carga mais comum em UPSs, sejam mais facilmente avaliados. Estas simulações, bem como as ferramentas desenvolvidas para quantificar as perdas nos conversores, são implementadas no *software* MA-TLAB/Simulink. Os resultados teóricos de perdas, estimados por estas ferramentas, são validados via medição elétrica em um protótipo de um conversor *buck*. Por fim, a efetividade da técnica calorimétrica para medição de perdas é demonstrada por meio da construção de um protótipo de calorímetro do tipo *indireto série*.

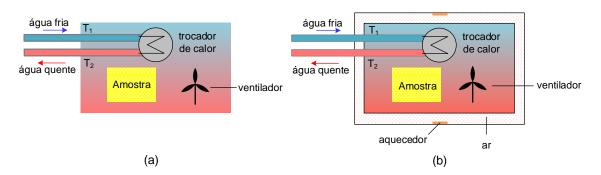

Figura 1.1 – Topologias trifásicas analisadas.

Topologias: (a) dois níveis, (b) NPC1 e (c) NPC2.

Fonte: Dados da pesquisa, 2016.

Assim, esta pesquisa acrescenta contribuições para o projeto de UPSs e de conversores estáticos em geral. As ferramentas propostas para o cálculo das perdas servem ao dimensionamento de conversores e à comparação teórica de filosofias de projeto, como já foi discutido. Estas ferramentas generalizam as análises térmicas para qualquer topologia de circuito e podem reduzir os tempos de projeto de conversores. Ademais, as análises e resultados desta pesquisa demonstram que o uso de dispositivos de SiC acena como solução potencial para o aumento do rendimento das UPSs. Por fim, este trabalho se insere no projeto de pesquisa e desenvolvimento (P&D) entre UFMG e Engetron, fabricante de UPSs e proponente deste projeto. Os resultados

desta pesquisa, portanto, já orientam esta empresa em parte das rotinas de dimensionamento dos componentes das UPSs.

O texto desta dissertação foi estruturado em seis capítulos. No capítulo 2, procede-se à revisão bibliográfica, para fundamentação e conceituação do trabalho. Neste capítulo, discutem-se inicialmente as categorias de UPSs e as vantagens e desvantagens de cada classe. As perdas dominantes nos conversores são definidas na sequência e as equações implementadas para o cálculo destas perdas são enumeradas. Em seguida, os métodos de medição de perdas mais usuais são caracterizados e as vantagens e desvantagens de cada técnica são pontuadas.

No capítulo 3, detalham-se as abordagens de modelagem e simulação da UPS de dupla conversão, adotadas nos estudos de rendimento conduzidos nesta dissertação. O capítulo 4 descreve as ferramentas implementadas para cálculo de perdas em conversores e os protótipos desenvolvidos para medição destas perdas. No capítulo 5, constam os resultados teóricos da pesquisa e os resultados experimentais preliminares. Por fim, o capítulo 6 discorre sobre as conclusões e as propostas de continuidade deste trabalho.

## 2 REVISÃO BIBLIOGRÁFICA

Este capítulo revisa a literatura básica que fundamenta este trabalho. Inicialmente, discutese sobre a classificação de UPSs. A UPS em estudo, do tipo dupla conversão, é então definida. Na sequência, as perdas assumidas dominantes em conversores são conceituadas. As equações e os métodos descritos na literatura para que estas parcelas dominantes sejam estimadas são apresentadas. Por fim, detalham-se os procedimentos usuais para medição de perdas, bem como aqueles adotados na presente pesquisa.

## 2.1 UPS: definição e classificação

As UPSs, acrônimo em inglês para *Uninterruptible Power Supplies*, são equipamentos que garantem a alimentação de subsistemas elétricos quando há interrupção no fornecimento de energia da rede principal. Estes equipamentos são usuais no suprimento de sistemas com missão crítica, em que falhas e interrupções podem levar a riscos e a perdas sociais ou financeiras. Como exemplo destes sistemas, citam-se: instrumentação médica de unidades de terapia intensiva (UTI); linhas de produção industriais; controladores de plantas de usinas nucleares; *datacenters*; servidores de sites de serviços de *e-mail* e *e-commerce*; equipamentos de aeroportos, centrais de telecomunicação e bolsas de valores, entre outros. Nestas aplicações, a taxa de disponibilidade de redes elétricas de distribuição comuns, estimada no máximo em 99,9%, é insuficiente para garantir a operação segura, sem riscos ou danos irreparáveis (CURTIS, 2011).

Por outro lado, na maior parte das aplicações críticas, os distúrbios de qualidade de energia típicos das redes de distribuição – como afundamentos, surtos, impulsos, sobretensões, subtensões, variações de frequência, distorções harmônicas, etc. – podem levar ainda a falhas e perdas. Segundo estimativas do Comitê Europeu de Fabricantes de Máquinas Elétricas e Equipamentos de Eletrônica de Potência (*European Committee of Manufacturers of Electrical Machines and Power Electronics*, CEMEP), cerca de 45 % das falhas em sistemas críticos se devem a interrupções ou a outros distúrbios na alimentação, como indica o gráfico da Figura 2.1 (CEMEP, 2008). Os custos por uma hora de indisponibilidade de alguns sistemas críticos, como redes de telefonia móvel, linhas de produção automotivas e centrais de transações de cartões de créditos, de reserva e venda de voos ou de bolsas de valores, também estimados pelo CEMEP, são enumerados na Figura 2.1. Estas perdas podem ser ainda humanas, no caso de falhas em sistemas vitais como hospitais e controladores de voo.

Nestas aplicações críticas, a simples adição de geradores ou fontes auxiliares de emergência não assegura a alimentação sustentada e contínua, já que a comutação para estas fontes não é instantânea (CURTIS, 2011). Neste contexto, portanto, o uso de UPSs, instaladas entre a

Causas de falhas Custos da indisponibilidade Atuação intempestiva da Falhas na Custos de 1h de Serviços alimentação 45 % proteção indisponibilidade Redes de telefonia móvel 40 mil euros Centrais de reservas de voos 90 mil euros Falhas em equipamentos 20 % Centrais de cartões de crédito 2,5 mi euros 6 mi euros Linhas de produção automotiva 6,5 mi euros Centrais de bolsas de valores Erros humanos

Figura 2.1 – Causas de falhas e custos da indisponibilidade de sistemas críticos.

Fonte: Adaptado de CEMEP (2008).

rede principal e a carga crítica, se torna mandatório. Assim, segundo EATON (2012), as UPSs assumem três funções básicas, na maior parte das aplicações:

- (i) a de prevenir danos que decorrem de surtos e transitórios casos em que as UPSs devem ser continuamente conectadas em série com a carga crítica;

- (ii) a de evitar perdas ou corrupção de dados em sistemas computadorizados, que resultam de desligamentos intempestivos;

- (iii) a de prover a disponibilidade e a continuidade de redes e de serviços durante o processo de *startup* de sistemas de alimentação auxiliares (como geradores a diesel).

De modo geral, todas as UPSs integram três unidades básicas, a saber: um módulo de armazenamento de energia, um estágio de conversão de energia e um sistema de monitoramento e controle (SANTOS FILHO, 1998), como representa a Figura 2.2. Assim, a estrutura de cada um destes elementos e o modo como estão conectados com a rede elétrica e com a carga crítica definem os critérios para a classificação das UPSs.

Módulo de armazenamento de energia

Módulo de conversão da energia

Chave de bypass

Módulo de monitoramento e controle

Figura 2.2 – Módulos básicos de uma UPS.

Fonte: SANTOS FILHO (1998).

O esquema da Figura 2.3 exibe as classes e subclasses de UPSs comumente definidas na literatura. De modo geral, as UPSs podem ser *estáticas*, *rotativas* ou *híbridas*. O primeiro tipo se

vale apenas de conversores estáticos, baseados em dispositivos semicondutores, para a conversão de energia. O segundo integra somente sistemas eletromecânicos com máquinas girantes, com geradores e motores acoplados. Já o terceiro tipo combina conversores estáticos e máquinas girantes (GUERRERO; VICUNA; UCEDA, 2007). As UPSs rotativas, categorizadas em *online* e *offline*, são brevemente descritas na subseção 2.1.1. A seção 2.1.2 apresenta a estrutura típica de uma UPS híbrida. Já as UPSs estáticas, subdivididas em passivas ou *offline*, *line-interactive* e de dupla conversão ou *online*, são discutidas na seção 2.1.3.

Rotativas Híbridas Estáticas

Online Offline Passivas ou offline interactive ou online

Figura 2.3 – Classificação das UPSs.

Fonte: Dados da pesquisa, 2016.

#### 2.1.1 UPSs rotativas

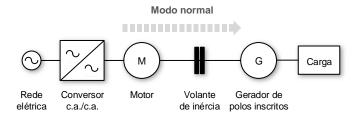

As UPSs rotativas, mais comuns no século passado, são ainda aplicáveis a sistemas de potências mais elevadas, da ordem de centenas de MW. Em linhas gerais, este tipo de UPS inclui um conjunto "motor-gerador" e volantes de inércia de massa elevada, que mantêm a carga crítica alimentada mesmo quando há interrupções da ordem de segundos na rede principal (GUERRERO; VICUNA; UCEDA, 2007). Há variações deste tipo de UPS que operam *online*, *i.e.*, continuamente conectadas às cargas críticas e *offline*, acionadas apenas quando há falhas na rede principal. A Figura 2.4 representa a configuração típica destes dois tipos de UPSs rotativas. Na UPS rotativa *online* da Figura 2.4(a), a rede principal alimenta um motor conectado a volantes de inércia e acoplado ao eixo de um gerador, que, por sua vez, alimenta continuamente as cargas críticas. Já na UPS rotativa *offline*, ilustrada na Figura 2.4(b), um "conjunto motor-gerador" opera em regime normal apenas para injeção de potência reativa (Q), como um compensador síncrono, para fins de correção de fator de potência. Quando há interrupção na rede principal, uma chave desconecta esta rede e aquele conjunto passa a fornecer também potência ativa (P) às cargas.

Como vantagens das UPSs rotativas, citam-se a confiabilidade e o baixo custo de manutenção, já que o sistema integra apenas componentes eletromecânicos (CURTIS, 2011). Ademais, estas UPSs também podem ser dimensionadas para a operação em médias tensões na entrada e na saída, sem elevar proibitivamente os custos – o que em geral ocorre nos sistemas com UPSs estáticas. A demanda por ventilação nas UPSs rotativas é também menor do que nas estáticas,

Modo normal -----Carga Rede Motor Volante Gerado elétrica de inércia (a) Modo normal ..... Carga Q Rede Chave elétrica estática Gerador P, Q Modo energia Volante armazenada de inércia Motor a diesel (b)

Figura 2.4 – Tipos de UPS rotativas.

Tipos: (a) online e (b) offline.

Fonte: Adaptado de Guerrero, Vicuna e Uceda (2007).

já que o sistema suporta temperaturas mais elevadas. Estas UPSs também permitem o uso de motores de combustão interna diretamente, via acoplamento mecânico com o gerador (CURTIS, 2011), em alternativa ao uso de baterias. Por fim, contrariamente às UPSs estáticas, as UPS rotativas dispensam a necessidade de filtros passivos no estágio de saída ou de entrada.

Todavia, como desvantagens das UPSs rotativas, salientam-se as perdas elevadas do conjunto "motor-gerador" – mais críticos nas UPSs *online*, os altos níveis de ruído introduzidos pelo sistema (GUERRERO; VICUNA; UCEDA, 2007) e o custo de aquisição, que supera em 20 % a 30 % os custos de uma UPS estática (CURTIS, 2011).

#### 2.1.2 UPSs híbridas

A combinação de UPSs rotativas com conversores estáticos resulta nas UPSs *híbridas*, representadas no diagrama da Figura 2.5. Nestas UPSs, um acionamento de velocidade variável, composto por um conversor c.a./c.a., ajusta a velocidade do motor conectado a um volante de inércia. Um gerador de "polos inscritos" (*written-pole*) alimenta a carga a uma frequência constante, mesmo com o rotor a velocidades entre 3150 e 3600 *rpm* (GUERRERO; VICUNA; UCEDA, 2007). No caso de interrupção na rede principal, o volante de inércia mantém o sistema em rotação a velocidades maiores do que 3150 *rpm* (GUERRERO; VICUNA; UCEDA, 2007), garantindo, assim, o suprimento da carga crítica. Em regime normal, o conjunto "motor-gerador" condiciona a tensão sobre a carga. O conversor c.a./c.a. permite ainda a atenuação de distorções harmônicas e a conversão da frequência de operação (*e.g.*, de 60 *Hz* para 50 *Hz*). Esta variação

de UPS combina, portanto, o armazenamento mecânico da energia, provido pelo volante de inércia, com a independência em frequência introduzida pelo conversor c.a./c.a.. Assim, as vantagens da UPS rotativa *online*, somadas à independência em frequência, se aplicam à UPS híbrida. A adição do conversor estático, todavia, penaliza a confiabilidade e os custos do sistema, em comparação com a UPS rotativa *online* típica da Figura 2.4(a). Como desvantagens da UPS híbrida também figuram o custo elevado, o peso e os níveis de ruído, bem como as perdas significativas ao longo dos estágios de conversão de energia.

Figura 2.5 – Diagrama esquemático de uma UPS híbrida.

Fonte: Adaptado de Guerrero, Vicuna e Uceda (2007).

#### 2.1.3 UPSs estáticas

As UPSs *estáticas*, contrariamente às rotativas e híbridas, constituem-se apenas de conversores estáticos. Segundo a norma IEC 62040-3 (2011), há três classes de UPSs estáticas, categorizadas conforme o modo como interagem com a rede principal e quanto à independência em tensão/frequência:

- (i) UPSs offline ou passivas, dependentes da tensão e da frequência da rede principal;

- (ii) UPSs *line-interactive*, independentes da tensão da rede principal, mas dependentes em frequência;

- (iii) UPSs *online* ou de dupla conversão, independentes da tensão e da frequência da rede principal.

Em geral, a análise dos distúrbios críticos para a planta define um critério inicial para a seleção de UPSs (GUERRERO; VICUNA; UCEDA, 2007). A Tabela 2.1 detalha os distúrbios que cada tipo de UPS estática pode prevenir e, assim, orienta a seleção de UPSs para uma aplicação em particular, conforme a sensibilidade da carga crítica.

Como se nota na Tabela 2.1, as UPSs do tipo passivas ou *offline* só corrigem, em regime normal, problemas associados a distúrbios com durações t maiores que  $4\,ms$  e menores que  $16\,ms$  (VILLAFÁFILA et al., 2007). Ao comutar para o modo de energia armazenada (com alimentação por baterias), estas UPSs corrigem interrupções sustentadas de duração t maior que  $10\,ms$ . Já as UPSs do tipo line-interactive previnem também variações de tensão de curta e de longa duração, como afundamentos, elevações, subtensões e sobretensões. Por fim, as UPSs de

|                  | Distúrbio                                                                                                                                     | <b>UPS</b> recomendada                            |                                        |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------|

|                  |                                                                                                                                               | Classe IEC                                        | Tipo                                   |

| 1<br>2<br>3      | Interrupção na rede de duração $t>10ms$ "Afundamento" de tensão com $4ms < t < 16ms$ "Elevação" de tensão com $4ms < t < 16ms$                | Dependente da tensão e<br>da frequência da rede   | Passiva<br>ou <i>offline</i>           |

| <b>4</b> 5       | Afundamento temporário ou momentâneo de tensão ou subtensão sustentada Elevação temporária ou momentânea de tensão ou sobretensão sustentada  | Independente da tensão<br>da rede                 | Line-<br>interactive                   |

| 6<br>7<br>8<br>9 | Transitórios, picos, impulsos, "afundamentos" e "elevações" de tensão de duração $t<4ms$ Variações de frequência Ruídos Distorções harmônicas | Independente da tensão e<br>da frequência da rede | Dupla<br>conversão<br>ou <i>online</i> |

Tabela 2.1 – Distúrbios de qualidade de energia e tipo de UPS para correção.

Fonte: Adaptado de Guerrero, Vicuna e Uceda (2007) e Villafáfila et al. (2007).

dupla conversão ou *online* suprimem todos estes distúrbios e ainda garantem a imunidade da carga crítica a transitórios e surtos com durações menores que  $4\,ms$ , a variações de frequência, a ruídos e a distorções harmônicas. O modo como cada uma destas classes de UPS estática interage com a rede elétrica e, assim, corrige os distúrbios enumerados na Tabela 2.1, é abordado nas subseções a seguir. As vantagens e desvantagens de cada tipo são também discutidas.

#### 2.1.3.1 UPS estáticas passivas ou offline

O diagrama esquemático de uma UPS passiva ou *offline* segue na Figura 2.6. Esta UPS constitui-se de um banco de baterias, um retificador, um inversor e uma chave. O banco de baterias, conectado em paralelo com a carga, provê o *backup* de energia, quando da indisponibilidade da rede principal. Este tipo de UPS pode assumir dois regimes de operação, como definem as normas: o modo normal e o modo de "energia armazenada" (tradução livre para o termo *stored-energy mode*).

Rede elétrica

Retificador

Figura 2.6 – Diagrama esquemático de uma UPS offline.

Fonte: Adaptado de Guerrero, Vicuna e Uceda (2007).

No modo normal, a carga crítica é alimentada pela rede principal e o banco de baterias, conectado à rede por um conversor c.a./c.c., é mantido em carga completa. Esta UPS pode incluir filtros de entrada ou outros recursos de condicionamento de tensão, que atenuam alguns distúrbios da rede principal. Todavia, não foram localizadas, na norma IEC 62040-3, referências específicas ao tipo de condicionamento que esta classe de UPS deve garantir. Mas há, no texto desta norma, a indicação de que "dispositivos adicionais podem ser incorporados para prover condicionamento de energia, *e.g.*, transformadores ferroressonantes ou de *tap* variável"<sup>1</sup>.

Já no modo de "energia armazenada", que ocorre quando a rede principal está indisponível, o sistema "banco de baterias + inversor" passa a alimentar a carga. A transição para este modo, quando da ocorrência da interrupção da rede, demanda até  $10\,ms$  (KARVE, 2000). A UPS continua a operar no estado de "energia armazenada" durante o período em que as baterias possam suprir a carga, referido na literatura como *backup time* (KARVE, 2000), ou até que a rede principal se restabeleça. Nesta última condição, a UPS deve retornar ao modo normal.

Como vantagens das UPSs *offline*, podem-se citar a simplicidade de projeto e o baixo custo e volume. Como contrapartida, todavia, figuram-se como desvantagens desta variação de UPS:

- (i) dependência com a tensão da rede e impossibilidade de regulação da tensão em modo normal;

- (ii) dependência com a frequência da rede, o que inviabiliza o uso desta UPS como conversor de frequência (de 60 Hz/50 Hz, por exemplo) ou a rejeição de distúrbios associados à variação de frequência (ruídos, distorções harmônicas, transitórios, etc.);

- (iii) tempos de chaveamento para o modo de "energia armazenada" elevados, que podem ser proibitivos em algumas aplicações com cargas mais sensíveis, como centrais de grandes computadores (KARVE, 2000);

- (iv) imunidade em modo normal apenas a distúrbios de subtensão ou sobretensão com duração maior do que 4 ms e menor do que 16 ms e vulnerabilidade a quaisquer outros distúrbios (GUERRERO; VICUNA; UCEDA, 2007);

- (v) modelos comerciais de potência nominal de até  $2\,kVA$ , em razão das limitações desta topologia de UPS (KARVE, 2000);

- (vi) uso não-recomendado em ambientes potencialmente ruidosos, com possíveis interferências ou com distúrbios de alimentação, como em plantas industriais (EATON, 2012).

A UPS *offline*, portanto, penaliza desempenho, funcionalidade e proteção contra distúrbios, para fins de redução dos custos. O baixo custo justifica o largo uso desta UPS em

<sup>&</sup>lt;sup>1</sup> Tradução livre do excerto da norma IEC 62040-3: "additional devices may be incorporated to provide power conditioning, e.g. ferroresonant transformer or automatic tap changing" (MGE, 1999).

aplicações residenciais típicas de cerca de  $600 \, VA$ , para alimentação de computadores pessoais (GUERRERO; VICUNA; UCEDA, 2007).

#### 2.1.3.2 UPS estáticas line-interactive

A Figura 2.7 ilustra a topologia de uma UPS *line-interactive*. Nesta topologia, um conversor em paralelo interage com a rede para carregar o banco de baterias e para condicionar a tensão sobre a carga. Assim, há, como no caso da UPS *offline*, dois estados de operação, a saber: o regime normal e o modo de "energia armazenada".

Chave Rede estática elétrica

Conversor bidirecional

Modo de energia armazenada

Figura 2.7 – Diagrama esquemático de uma UPS line-interactive.

Fonte: Adaptado de Guerrero, Vicuna e Uceda (2007).

No modo normal, a carga é alimentada pela associação paralela da rede principal com um inversor, que serve ao condicionamento da tensão de saída – como um filtro ativo. Este inversor, que também opera como retificador, mantém o banco de baterias continuamente carregado, em regime normal (GUERRERO; VICUNA; UCEDA, 2007).

No modo de "energia armazenada", que ocorre quando há interrupção ou falhas na rede principal, o inversor e a bateria passam a alimentar continuamente a carga. Uma chave estática desconecta a rede principal da carga. Este estado perdura até que as baterias se descarreguem (*backup time*) ou até que a rede retorne aos níveis seguros de operação da UPS. Neste último caso, a UPS retoma o estado normal.

A vantagem desta variação de UPS é o baixo custo, quando comparada a UPSs *online* de mesma potência. Todavia, ressaltam-se, como desvantagens das UPSs *line-interactive*:

- (i) dependência com a frequência da rede, o que inviabiliza o uso desta UPS para conversão de frequências (de 60 Hz/50 Hz, por exemplo) ou a rejeição de distúrbios associados à variação de frequência (ruídos, distorções harmônicas, transitórios, etc.), em regime normal;

- (ii) vulnerabilidade a transitórios, ruídos, surtos e distorções harmônicas (GUERRERO; VICUNA; UCEDA, 2007);

- (iii) degradação de eficiência no caso em que carga exibe comportamento não-linear (KARVE, 2000);

- (*iv*) condicionamento de tensão limitado, já que o inversor opera em paralelo com a rede principal (KARVE, 2000);

- (v) potência máxima de até 5 kV A (GUERRERO; VICUNA; UCEDA, 2007), como resultado das limitações desta topologia de UPS.

A dependência em relação à frequência da rede torna o uso da UPS *line-interactive* inviável para a alimentação de cargas sensíveis de potências elevadas (KARVE, 2000). Assim, estas UPSs só são comumente aplicadas em sistemas de  $0, 5\,kVA$  a  $5\,kVA$ , *e.g.*, de pequenos servidores (GUERRERO; VICUNA; UCEDA, 2007). Quando a rede principal é livre de distúrbios, o rendimento típico deste conversor atinge cerca de  $97\,\%$  (GUERRERO; VICUNA; UCEDA, 2007).

### 2.1.3.3 UPS estáticas de dupla conversão ou online

O diagrama da Figura 2.8 ilustra uma UPS de dupla conversão. Nesta topologia, um conversor c.a./c.a. se conecta continuamente em série com a carga crítica, em regime normal. Esta UPS pode assumir três regimes de operação: o modo normal, o modo de "energia armazenada" (stored-energy mode) e o modo bypass.

Modo bypass

Chave estática

de bypass

Modo normal

Rede

elétrica

Retificador

Reti

Figura 2.8 – Diagrama esquemático de uma UPS de dupla conversão.

Fonte: Adaptado de Guerrero, Vicuna e Uceda (2007).

Em regime normal, um conversor c.a./c.a., com estágios retificador e inversor em cascata, supre continuamente a carga e condiciona a tensão e a frequência de alimentação. A combinação dos dois estágios de conversão fundamentam o termo em inglês *double-conversion*, mais aceito pela norma IEC para designar esta classe de UPS. Esta dupla conversão torna a UPS independente da tensão e da frequência da rede principal. Ainda em regime normal, o retificador – ou, eventualmente, um conversor c.c./c.c. adicional, para ajustar os níveis de tensão e corrente (LEGA et al., 2007) – mantém a bateria em carga máxima.

No modo de "energia armazenada", em que a rede principal não atende aos níveis de tolerância da UPS ou se torna indisponível, o banco de baterias e o inversor passam a prover a carga. A UPS se mantém neste estado durante o *backup time* ou até que a rede volte a operar em condições normais.

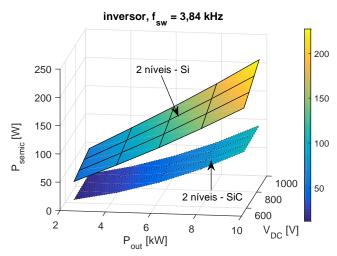

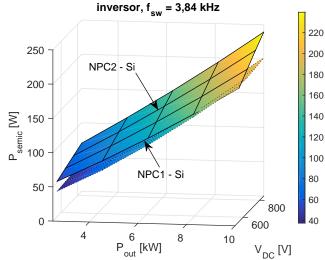

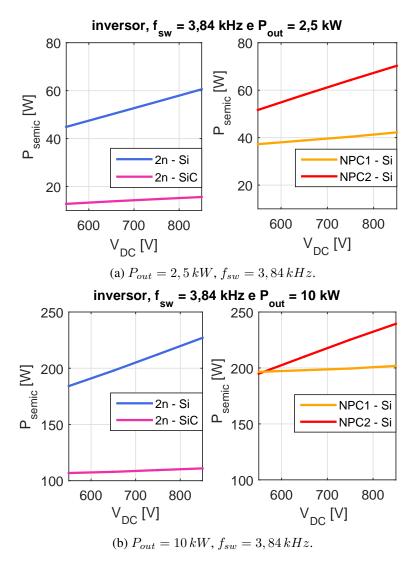

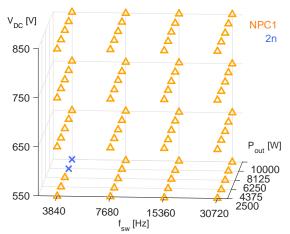

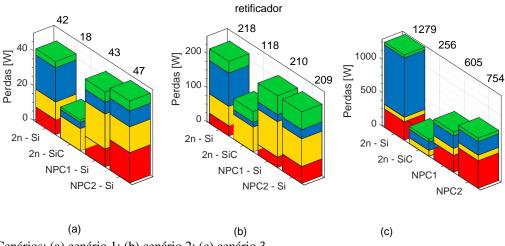

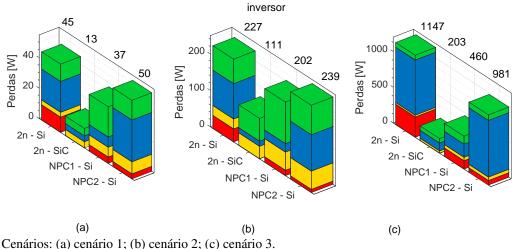

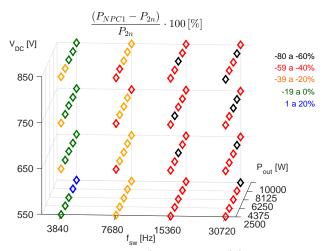

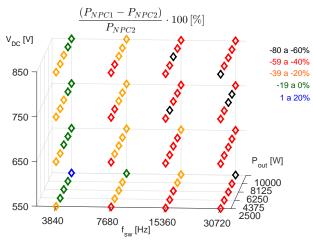

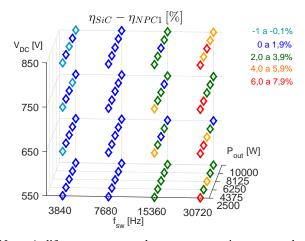

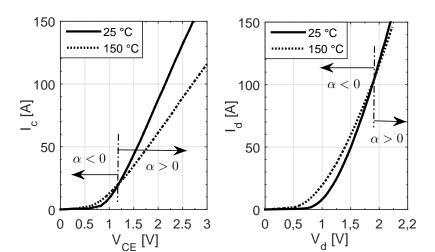

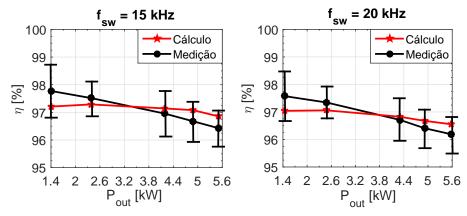

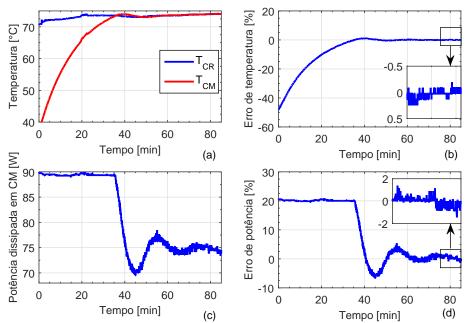

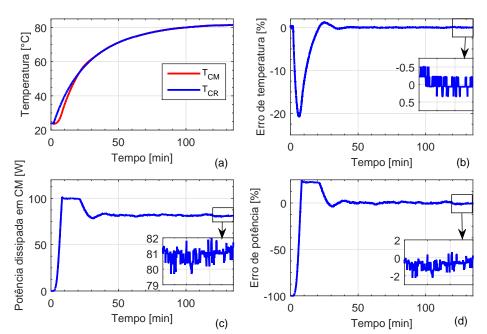

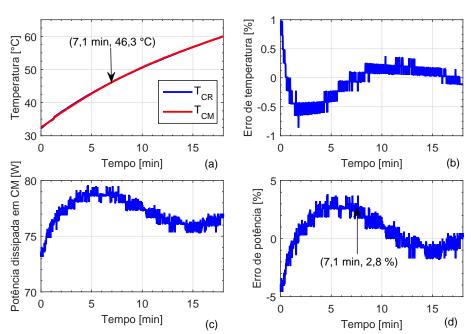

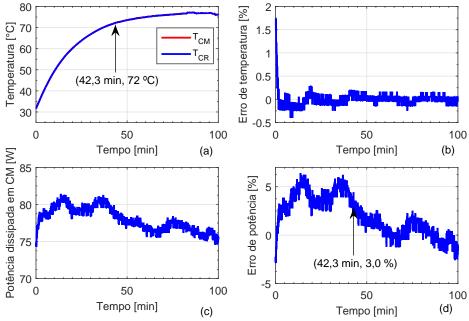

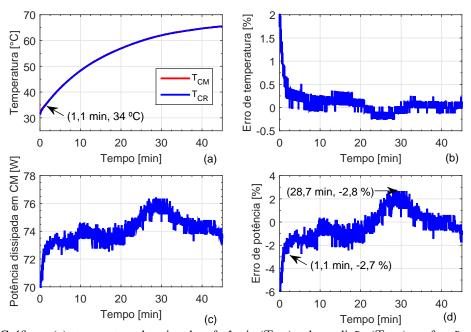

No modo *bypass*, uma chave estática estabelece um curto-circuito entre a entrada e a saída da UPS, permitindo a alimentação da carga diretamente pela rede principal. Em geral, a UPS assume este estado em caso de sobrecarga ou de transitórios de corrente na carga, de fim do *backup time* (KARVE, 2000) ou ainda, quando há falhas na UPS. No instante de comutação para o modo *bypass*, a UPS garante o sincronismo da tensão da carga com a rede principal (KARVE, 2000). Todavia, se a frequência da carga diferir da frequência da rede principal, o *bypass* via chave não se torna possível. Por outro lado, se os níveis de tensão da carga não equivalerem aos da rede principal, a chave de *bypass* pode incluir um transformador, para viabilizar esta conexão (KARVE, 2000).