# HYBRID CODE PLACEMENT FOR HETEROGENEOUS ARCHITECTURES

### MARCELO PEREIRA NOVAES

# HYBRID CODE PLACEMENT FOR HETEROGENEOUS ARCHITECTURES

Dissertação apresentada ao Programa de Pós-Graduação em Ciência da Computação do Instituto de Ciências Exatas da Universidade Federal de Minas Gerais como requisito parcial para a obtenção do grau de Mestre em Ciência da Computação.

### Orientador: Fernando Magno Quintão Pereira

Belo Horizonte Fevereiro de 2018

### MARCELO PEREIRA NOVAES

# HYBRID CODE PLACEMENT FOR HETEROGENEOUS ARCHITECTURES

Dissertation presented to the Graduate Program in Ciência da Computação of the Universidade Federal de Minas Gerais in partial fulfillment of the requirements for the degree of Master in Ciência da Computação.

Advisor: Fernando Magno Quintão Pereira

Belo Horizonte February 2018 © 2018, Marcelo Pereira Novaes Todos os direitos reservados

### Ficha catalográfica elaborada pela Biblioteca do ICEx - UFMG

| Novaes, Marcelo Pereira                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N935h Hybrid code placement for heterogeneous<br>Architectures / Marcelo Pereira Novaes. — Belo<br>Horizonte, 2018.<br>xx, 58 f.: il.; 29 cm.                                          |

| Dissertação (mestrado) - Universidade Federal<br>de Minas Gerais – Departamento de Ciência da<br>Computação.                                                                           |

| Orientador: Fernando Magno Quintão Pereira<br>Coorientador: Vinicius Tavares Petrucci                                                                                                  |

| <ol> <li>Computação – Teses. 2. Compiladores<br/>(Computadores). 3. Arquitetura de computador.</li> <li>I. Orientador. II. Coorientador. III. Título.<br/>CDU 519.6*33(043)</li> </ol> |

#### UNIVERSIDADE FEDERAL DE MINAS GERAIS INSTITUTO DE CIÊNCIAS EXATAS PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

### FOLHA DE APROVAÇÃO

Hybrid Code Placement for Heterogeneous Architectures

### MARCELO PEREIRA NOVAES

Dissertação defendida e aprovada pela banca examinadora constituída pelos Senhores:

PROF. FERNANDO MAGNO QUINTÃO PEREIRA - Orientador Departamento de Ciência da Computação - UFMG

PROF. VINICIUS TAVARES PETRUCCI - Coorientador Departamento de Ciência da Computação - UFBA

DR. ABDOULAYE GAMATIÉ Centre National de la Recherche Scientifique - LIRMM

PROF. ADRIANO ALONSO VELOSO Departamento de Ciência da Computação - UFMG

Belo Horizonte, 23 de fevereiro de 2018.

## Acknowledgments

Em relação a minha dissertação:

- A Universidade de Minas Gerais, pela aceitação no programa, e a CAPES pelo financiamento durante o mestrado. To the CONTINUUM project for funding my scientific endeavors while in Montpellier, France.

- Ao Fernando, que me aceitou, orientou e o qual eu me inspiro ao ve-lo conciliar: resultado, talento, disciplina, e cuidado com as pessoas.

- Ao Vinicius, que aceitou ser meu co-orientador e me direcionou no projeto em muitas oportunidades.

- To the professor Abdoulaye, that believed in our project, hosted me on his lab and joined us in this journey.

- Ao professor Renato Assunção, que me deu liberdade de explorar e escolher qualquer projeto, em qualquer área, mesmo que dessa escolha decorresse a troca de orientador.

- Ao LaC, Laboratório de Compiladores, que é uma família e me aceitou de braços abertos. A todos do ninho (the-dragon-nest).

- Ao professor Adriano que aceitou fazer parte da banca de avaliação.

- A todos os funcionários da UFMG/UFBA/LIRMM que me ajudaram, como o pessosal do CRC/UFMG, a Sônia da UFMG, e a Caroline Lebrun do LIRMM.

Em relação ao lado pessoal:

- Aos meus pais, Celia e Francisco, que sempre me dão apoio em minhas escolhas. A minha irmã Luisa, por ser minha grande companheira nessa vida acadêmica. A minha irmã Leila que dará luz em breve a minha sobrinha Fernanda. A toda a minha família de Belo Horizonte que me acolheu pelo período do mestrado.

- Aos meus amigos, que fazem a vida mais leve, de Salvador, Belo Horizonte e Montpellier. Em especial ao meu primo André, que sempre me apoia e ajuda nas decisões mais importantes e ao Caio, que foi de Salvador para o laboratório.

À todos que de alguma maneira contribuiram para a realização dessa dissertação, meu muito obrigado! Je remercie tous ceux qui, d'une manière ou d'une autre, ont contribué à la éussite de ce travail!

To all those who helped to the elaboration of this master's dissertation in any way, thank you!

## Abstract

Modern computer architectures are becoming each day more heterogeneous. This heterogeneous design emerges through the combination, within the same hardware, of several different processors. Choosing the best hardware configuration for a given program is difficult, because programs, even of moderate size, go through many phases during execution. These phases benefit differently from the same hardware configuration. Researchers have used a plethora of techniques to deal with this problem, but two techniques seem to standout: dynamically or statically. The former is implemented at the runtime level, be it through an operating system or a scheduler/middleware. The latter is implemented at compilation level. In this dissertation, we investigate the mixing of both approaches achieving a synergy that, otherwise, could not be attained by each technique individually. On this new scheme, we propose an instrumentation framework that produces an adaptive program that uses both source-code and run-time information to make decisions. We have implemented our instrumentation framework in the LLVM compiling infrastructure. To demonstrate that our proposal is useful and effective, this master's dissertation compares this new code generator, called Astro, with state of the art approaches. The goal was reducing the energy consumption of programs while maintaining performance constraints. We evaluate on applications among different benchmarks and embedded boards.

**Keywords:** Compilers, heterogeneous architectures, energy-efficient systems, adaptive programs, non-assisted instrumentation, machine learning, classification, LLVM.

## Resumo

Arquiteturas de computadores modernas estão se tornando a cada dia mais heterogêneas. Essa heterogenidade emerge da possibilidade de combinação, dentro de um mesmo dispositivo, de diferentes tipos de processadores. Escolher a melhor configuração desses processadores é uma tarefa difícil, porque programas, mesmo em tamanhos moderados, apresentam diferentes fases durante a sua execução. Essas fases se beneficiam de forma diferente do dispositivo. Pesquisadores vêm utilizando diversas técnicas para lidar com o problema, mas duas delas se destacam: a dinâmica e a estatica. A primeira é implementada em tempo de execução, seja por um sistema operacional ou um escalonador. A última é implementada em tempo de compilação. Nessa dissertação, nós investigaremos a mescla das duas abordagens de modo a conseguir uma sinergia a qual não seria obtida por cada uma das técnicas individualmente. Nesse novo esquema, nós usamos uma ferramenta de instrumentação que cria programas que se migram sozinhos usando ambas informações retiradas do código fonte e informações coletadas em tempo de execução para fazer as decisões. Nós implementamos a ferramenta de instrumentação na infraestrutura de compilação LLVM. Para demonstrar que nossas ideias são úteis e efetivas, essa dissertação de mestrado compara esse novo gerador de código, chamado Astro, com abordagens no estado-da-arte, o utilizando para reduzir o consumo de energia (mantendo restrições de performance) em conjuntos de aplicações entre diferentes placas embarcadas.

**Palavras-chave:** compiladores, arquiteturas heterogêneas, economia de energia, programas adaptativos, instrumentação de código automática, aprendizagem por reforço, LLVM.

# List of Figures

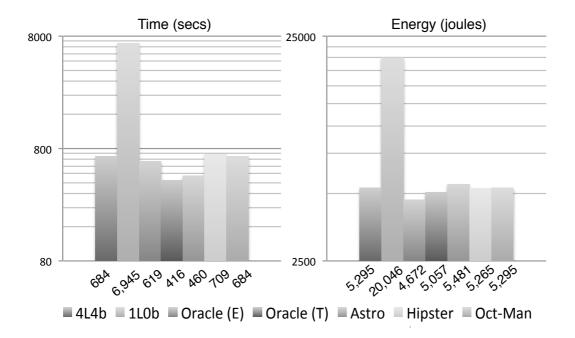

| 1.1 | Energy vs Processing time spent by two PARSEC benchmarks using simsmall inputs. The notation $xLyB$ denotes $x \perp IITTLE$ cores, and $y \perp big$ cores.                                                                                                                  | 5  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

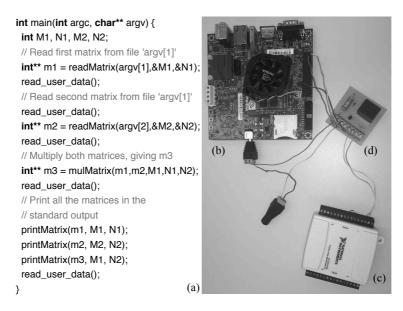

| 1.2 | (a) Simple matrix multiplication implemented in C. (b) The Nvidia TK1 board. (c) NI 6009 Data Acquisition Device. (d) Synchronization circuit                                                                                                                                 | 7  |

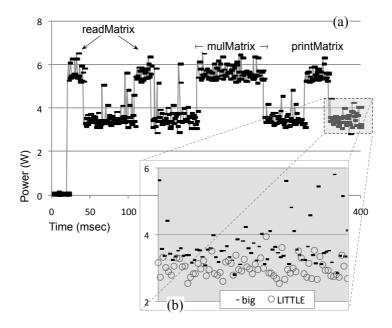

| 1.3 | (a) Power profile of program seen in Figure 1.2. The NI 6009 sample rate was 1000 samples/sec. (b) Zoom of the power profile obtained during the last phase of the program. We show power data obtained using one low-frequency core (Low), and using one ARM A15 core (High) | 8  |

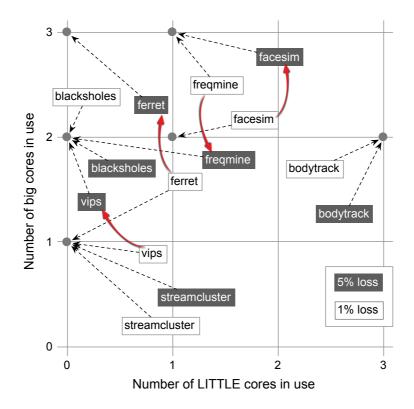

| 1.4 | Best configurations for seven PARSEC applications, given an acceptable slowdown of $1\%$ or $5\%$ compared to fastest configuration                                                                                                                                           | 9  |

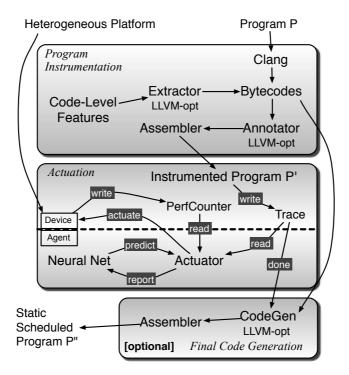

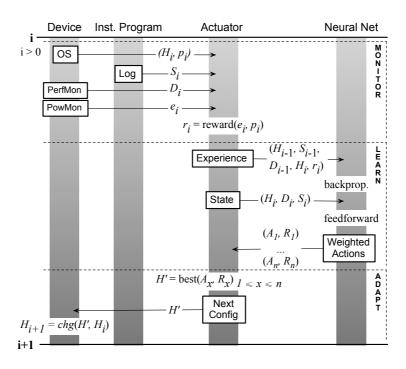

| 3.1 | The Astro Framework.                                                                                                                                                                                                                                                          | 22 |

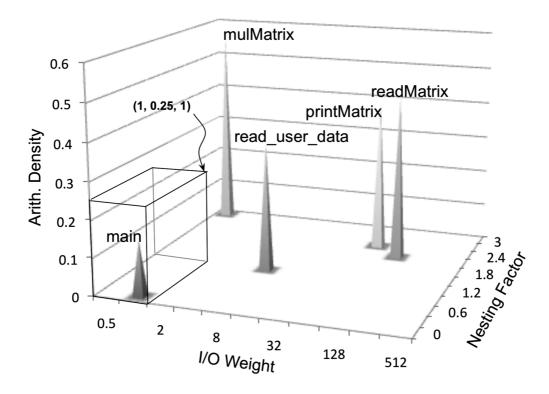

| 3.2 | Mapping the functions in Figure 1.2 (a) to program phases. $\ldots$                                                                                                                                                                                                           | 26 |

| 3.3 | The Actuation Algorithm.                                                                                                                                                                                                                                                      | 29 |

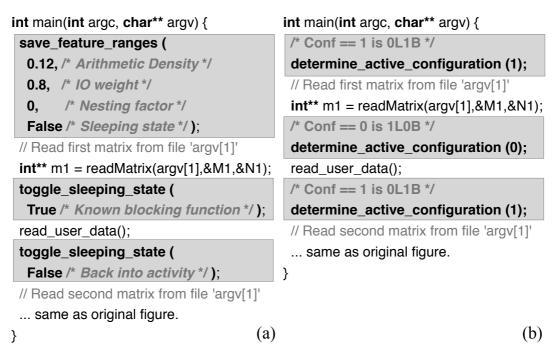

| 3.4 | (a) Instrumentation to mine features. (b) Final instrumentation, inserted in production code                                                                                                                                                                                  | 31 |

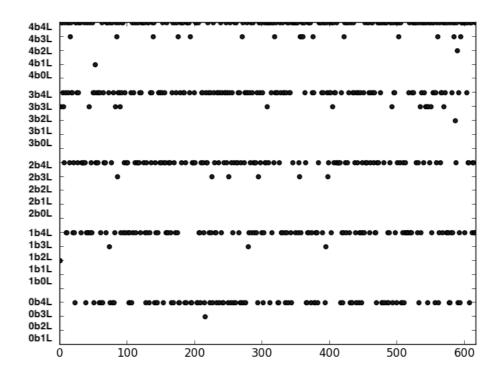

| 4.1 | Simulated approximated optimal policy for fluidanimate. The Y-axis repre-<br>sents different hardware configurations. The X-axis shows the application's<br>execution time in seconds.                                                                                        | 39 |

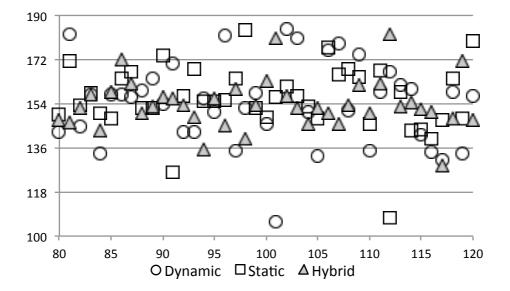

| 4.2 | Comparison between Astro and other 6 strategies                                                                                                                                                                                                                               | 40 |

| 4.3 | Supervised Learning applied to the fluidanimate application from PARSEC benchmark in an action space of 24 possible combinations of heterogeneous cores. Three learning models that achived the best results of the five tested:                                              |    |

|     | Gaussian Process Classifier, the Multi-layer Perceptron (MPL), the kNN                                                                                                                                                                                                        | 42 |

| 4.4 | Supervised learning applied to the 10 different phases of the Meabo micro-                                                   |    |

|-----|------------------------------------------------------------------------------------------------------------------------------|----|

|     | benchmark [ARM-software]. Fixing the best model for the three approaches,                                                    |    |

|     | that were the same (the GPC in the hybrid had also the same precision as the                                                 |    |

|     | Gaussian Naive Bayes). Part (a) of the Figure shows the result considering                                                   |    |

|     | three dynamic features (relative CPU load to the number of used cores,                                                       |    |

|     | instruction per cycles and cache miss ratio), (b) shows the result using 16                                                  |    |

|     | static features. The (c) shows the result of the hybrid approach, combining                                                  |    |

|     | both features                                                                                                                | 44 |

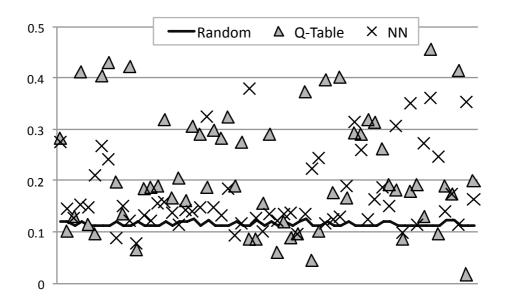

| 4.5 | Comparison between three different implementations of Astro. They vary                                                       |    |

|     | in the way they choose information to feed the neural-network. Dynamic:                                                      |    |

|     | uses only hardware phases (Definition 3.2.3); Static: uses only program                                                      |    |

|     | phases (Definition 3.2.2); Hybrid: uses both phases. Each dot along the                                                      |    |

|     | X-axis represents one execution of fluidanimate. The Y-axis represents the                                                   |    |

|     | maximum reward observed in that execution. We keep the state of the                                                          |    |

|     | neural-network across executions, so that it can learn. We show results                                                      |    |

|     | after 80 of such "episodes".                                                                                                 | 46 |

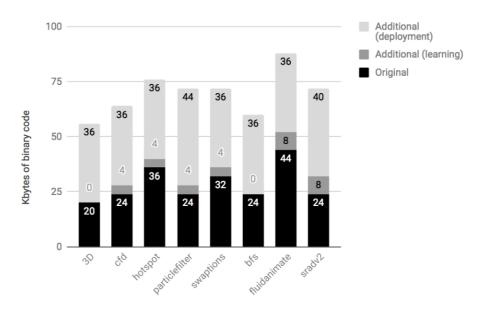

| 4.7 | This figure shows the binary code size on different applications. The Y-axis                                                 |    |

|     | represents the size in Kybtes. The X-axis represents the different applica-                                                  |    |

|     | tions. Plot shows from the original size in black, learning library adds in                                                  |    |

|     | gray and deploy adds in light gray. Binary size computed via the "du -h"                                                     |    |

|     | $command. \dots \dots$ | 49 |

|     |                                                                                                                              |    |

## List of Tables

19

# Contents

| A        | cknov | wledgn  | nents                                                              | ix        |

|----------|-------|---------|--------------------------------------------------------------------|-----------|

| A        | bstra | ct      |                                                                    | xi        |

| R        | esum  | 0       |                                                                    | xiii      |

| Li       | st of | Figure  | es                                                                 | xv        |

| Li       | st of | Tables  | S                                                                  | xvii      |

| 1        | Intr  | oducti  | ion                                                                | 1         |

|          | 1.1   | Contri  | ibutions                                                           | 3         |

|          | 1.2   | Empir   | ical Observation                                                   | 3         |

| <b>2</b> | Lite  | rature  | Review                                                             | 13        |

|          | 2.1   | Handl   | ing the Code Placement Problem                                     | 13        |

|          |       | 2.1.1   | The Static solution: decision at compiling time                    | 13        |

|          |       | 2.1.2   | The Dynamic solution: decision at running time                     | 15        |

|          |       | 2.1.3   | Hybrid Motivation: Static vs Dynamic decisions                     | 15        |

|          |       | 2.1.4   | The Hybrid: combining Dynamic and Static information               | 17        |

|          |       | 2.1.5   | Trade-offs                                                         | 18        |

|          | 2.2   | Non-a   | ssisted code-placement                                             | 19        |

| 3        | Ast   | ro fran | nework                                                             | <b>21</b> |

|          | 3.1   | Reinfo  | preement learning via Q-Learning                                   | 22        |

|          | 3.2   | Comp    | onents of the Astro framework                                      | 24        |

|          |       | 3.2.1   | Part 1: Phase Partitioning                                         | 24        |

|          |       | 3.2.2   | Part 2: Actuation                                                  | 29        |

|          |       | 3.2.3   | Part 3: Final Code Generation                                      | 32        |

|          | 3.3   | Relati  | onship between Astro and the most related work $\ . \ . \ . \ .$ . | 33        |

| 4  | 4 Evaluation 37        |                                      |                 |

|----|------------------------|--------------------------------------|-----------------|

|    | 4.0.1                  | Experimental Setup                   | 37              |

|    | 4.0.2                  | Results in the Simulated Environment | 38              |

|    | 4.0.3                  | Results in an Actual Device          | 45              |

|    | 4.0.4                  | Overhead analysis                    | 47              |

| 5  | Conclusion<br>5.1 Open | n<br>questions and clarifications    | <b>51</b><br>51 |

| Bi | Bibliography 55        |                                      |                 |

# Chapter 1

# Introduction

Modern computer architectures are becoming each day more heterogeneous [62]. This heterogeneous design emerges through the combination, within the same hardware, of several different processors, such as big/little multi-core Central Processing Units (CPUs) [13][23], Graphics Processing Units (GPUs) [42] and Digital Signal Processors (DSPs) [49]. An advantage of this design is the possibility of allocating to each application the hardware configuration that best suits it. A hardware configuration consists of a number of cores, their type and their frequency level. We say that a configuration  $H_1$  suits a program better than another configuration  $H_2$  if  $H_1$  runs the program more efficiently than  $H_2$ , according to some metric such as runtime or energy consumption. Nevertheless, even though we have today the possibility of choosing among several configurations, the one that better fits the needs of a certain program, we still have no clear technique to perform this choice seamlessly.

Often a program has regions of code that benefit differently from distinct processors. We call the task of allocating program parts to processors the *code placement problem*. Typically, there are two ways to solve this problem: dynamically, or statically. Dynamic approaches [38; 44; 46] are implemented at the runtime level, be it through an operating system, a middleware or changes in the target program itself. Static approaches [25; 39; 45; 58] are implemented at the compiler level. The main advantage of the dynamic approach is the fact that it can take advantage of runtime information to improve the quality of the choices it makes. Static techniques, in turn, provide reduced runtime cost and better leverage of program characteristics. In this dissertation, we claim that it is possible to join these two approaches, achieving a synergy that, otherwise, could not be attained by each technique individually.

To fundament this claim, we show a few techniques to mix static and dynamic information and discuss a few others. Our final approach starts from a technique that has been already proven effective to schedule computations in heterogeneous architectures: *Reinforcement learning*. Nishtala *et al.* [44] have shown that reinforcement learning helps in finding good hardware configurations to applications subject to varying dynamic conditions. The beauty of this approach is adaptability: the same principles provide the means to explore a vast universe of states, formed by different hardware setups and runtime data changing over time. Given enough time, well-tuned heuristics let the learning algorithm find a set of scheduling decisions that that suits the underlying hardware. Yet, "enough time" can be too much time. The universe of possible runtime states is unbounded, and program behavior is hard to predict without looking into its source code. To speedup convergence, we bring the compiler into the fray.

The compiler gives us two benefits. First, it lets us mine program features, which we can use to train the learning algorithm. Second, it lets us instrument the program. This instrumentation allows the program itself to provide feedback to the scheduler, concerning the code region currently under execution. Based on previous knowledge, collected statically, about characteristics of that region, the scheduler can take immediate action. An action consists in choosing a new state to represent program behavior, and collecting the reward related to that choice. Such feedback is then used to fine-tune and improve scheduling decisions. As we show in Section 4, convergence is faster, and runtime smaller when deciding for static and dynamic combination of information on the state representation.

To validate our ideas, we have materialized them into a framework to instrument and execute applications in heterogeneous architectures: the *Astro System*. To collect static program characteristics, and instrument code, we use the LLVM compilation infra-structure [35]. We show that this new code generator is able to reduce the energy consumption of programs running on an Odroid XU4 architecture. Our experimental results, obtained in well known diverse benchmarks, show that we can achieve energy savings of up to 8%, when compared to state-of-the-art techniques, such as Hipster [44]. Such numbers result from the following contributions:

- **Observations:** in Section 1.2, we demonstrate that the different parts of a program, i.e., syntactic regions within its code, are an important factor determining its performance, in terms of speed and energy, when running on a heterogeneous hardware. This observation points us to the key insight: the possibility of augmenting an adaptive runtime apparatus with awareness of program characteristics.

- **Compiler:** in Section 3.2.1, we explain how to collect and discretize program features, and in Section 3.2.2, we explain how to instrument a program, so to use said features to fine-tune an adaptive code placement algorithm. The choice of program

features and runtime characteristics that this apparatus requires are also original contributions of this work.

**Runtime:** in Section 3.2.3, we show how to integrate the static information that we collect with a runtime environment that adapts to the environment. We offload the learning process to a server. Hence, runtime adaptation does not burden the application after it stabilizes. The process is gradual: if necessary to learn more, we reconnect the device to the server.

### 1.1 Contributions

This dissertation will present an overview of the code placement problem and introduce the Astro framework which:

- 1. Creates an adaptive program that migrates by itself, without human or scheduler intervention.

- 2. Exploits both source code and run-time information to decide for the best choice, achieving a synergy that only with one of them wasn't possible.

- 3. Evaluates different learning approaches as supervised, for a simplified space problem, and reinforcement learning techniques for a larger space problem.

- 4. To the best of our knowledge, Astro is the first system that feeds a learning model with both static and dynamic information to solve the placement of computations in a heterogeneous device.

**Awards:** A fork proposal of the Astro project, called "Intelligent DVFS"<sup>1</sup> [Int], has earned a Google Research Award for Latin America 2017 [Goo]. So, since August 2017, the lab has receiving funding from Google Inc. The project is an implementation of the method targeting mobile devices with the Android Operating System. The project is executed by Fernando (advisor) and Junio (a first year master student in our lab).

### 1.2 Empirical Observation

We motivate our work by presenting and discussing observations obtained from running a few experiments. First, we find that different hardware configurations yield

$<sup>^{1}\</sup>mathrm{It}$  was one of 27 approved projects from 281 proposals were submitted from nine different countries in Latin America.[Goo]

very different tradeoffs between power consumption and runtime speed for a program (Fig. 1.1). As a second observation, we notice that this behavior happens because programs have *power phases*: depending on the operations that they perform, they might consume more or less power per time unit (Fig. 1.2). Finally, we observe that the best hardware configuration for a program might not suit the needs of a different application (Fig. 1.4). Central to the discussion in this section is the notion of a *hardware configuration*:

**Heterogeneous architectures** Heterogeneous Computing (HC) was defined as "the well-orchestrated and coordinated effective use of a suite of diverse high-performance machines (including parallel machines) to provide superspeed processing for computationally demanding tasks with diverse computing needs. An HC system includes heterogeneous machines, high-speed networks, interface" [32]. Over the time, the heterogeneity was extended at different levels such as inside the same computer. So, HC, later called Heterogeneous Architectures, could be broadly defined as "the use of different processing cores to maximize performance" [11]. Recent architectures have a different type of cores integrated into the same chip. It is usually organized by clusters. One example used in this dissertationâs evaluation are Heterogeneous Processors of the ARM vendor, known as ARM Big.LITTLE processors.

**Definition 1.2.1 (Hardware Configuration)** A heterogeneous architecture is formed by a set  $P = \{p_1, p_2, \ldots, p_n\}$  of n processors. A hardware configuration is a function  $H : P \mapsto Boolean$ . If  $H(p_i) =$ **True**, then processor  $p_i$  is said to be active in H, otherwise it is said to be inactive.

The Universe of Hardware Configurations We observe that the same application might benefit differently from different hardware configurations. This benefit is measured in terms of processing time and energy consumption. Figure 1.1 illustrates this fact. The figure shows how two benchmarks from the PARSEC suite – Freqmine and Streamcluster – fare on an Odroid XU3/XU4 board<sup>2</sup>. This hardware features 4 Cortex-A15 2.0Ghz cores and 4 Cortex-A7 1.4Ghz cores. Following a nomenclature adopted by ARM, we shall call the A15 cores *bigs*, and the A7 cores *LITTLEs*. By switching on and off the different cores, we have 24 different hardware configurations<sup>3</sup>

<sup>&</sup>lt;sup>2</sup>Both XU3 and XU4 adopt the same Samsung Exynos 5422 big.LITTLE ARM processor

<sup>&</sup>lt;sup>3</sup>We have  $24 = 5 \times 5 - 1$  configurations, because we do not count the setup in which all cores are off.

Figure 1.1. Energy vs Processing time spent by two PARSEC benchmarks using simsmall inputs. The notation xLyB denotes  $x \perp ITTLE$  cores, and  $y \perp ig$  cores.

Each dot in the figure represents the average of 10 executions on the same configuration, using the smallest<sup>4</sup> input available in PARSEC. Variance is almost negligible, staying under 1% in every sample, for the two benchmarks. The X-axis shows the sum of the execution times of processors active in a particular configuration; hence, it is not clock time. Energy is measured with the Odroid XU3 on-board power measurement circuit and refers to work performed within the processors only; thus, peripherals are not considered.

Figure 1.1 lets us conclude that the energy and runtime footprint of applications vary greatly across different hardware configurations. For instance, the most time efficient configuration for Freqmine is 0L4B, i.e., four bigs and no LITTLEs (2.90secs,

<sup>&</sup>lt;sup>4</sup>This experiment takes approximately 12 days using the largest inputs.

10.43J). However, the most energy efficient configuration is 4L0B (4.01secs, and 8.65J). Results are not the same for Streamcluster. The best energy configuration is 0L1B (0.48secs, 0.69J). This is also the most time efficient configuration. Freqmine shows more parallelism than Streamcluster; therefore, it benefits more from a larger number of cores. This diversity of scenarios happen because programs have different computing scnearios (program *phases*). Energy and runtime behavior are similar within the same phase, and potentially different across different phases.

**Program phases** The instantaneous power consumed by a program is not always constant. In other words, a program has *power phases*. To demonstrate this fact, we shall consider the program in Figure 1.2 (a). This is an artificial example, which we have crafted to emphasize the different phases that a program undergoes during its execution. This program performs the following actions: (i) read two matrices from text files; (ii) multiply them and (iv) prints all the matrices in the standard output. In between each of these actions we have interposed commands to read data from the standard input.

Figure 1.3 shows the power profile of this program. This chart has been produced with JetsonLeap [7], an apparatus that let us measure the energy consumed by programs running on the Nvidia TK1 Jetson board<sup>5</sup>. JetsonLeap is formed by three components: the target Nvidia board (Figure 1.2 (b)), a data acquisition device, which reads the instantaneous power consumed by the board (Figure 1.2 (c)), and a synchronization circuit, which lets us communicate to the power meter which program event is running at each instant (Figure 1.2 (c)).

Distinct phases exist within the same program because it might use the hardware resources differently, depending on which part of it is running. By reading performance counters, we know that during matrix multiplication, CPU is at is maximum usage. During the input/output operations, this utilization drops slightly, and other components of the hardware, such as its serial port, are more exercised instead. This fall is steep once the program is waiting for user inputs. The CPU is not the only hardware component that accounts for power dissipation. The JetsonLeap apparatus measure energy for the entire hardware. Thus, the under utilization of the CPU does not mean that overall power consumption will decrease. Nevertheless, variations in the CPU usage are likely to cause variations in the power profile of the program.

<sup>&</sup>lt;sup>5</sup>In this section we use two different experimental setups: Odroid XU4 and Tegra TK1. The former gives us the richness of configurations seen in Figure 1.1. This diversity is absent on the latter, that has only one LITTLE core. However, the TK1 board gives us access to JetsonLeap, and, consequently, the ability to measure energy per programming events.

#### 1.2. Empirical Observation

**Figure 1.2.** (a) Simple matrix multiplication implemented in C. (b) The Nvidia TK1 board. (c) NI 6009 Data Acquisition Device. (d) Synchronization circuit.

Discovering such program phases by means of purely dynamic techniques is possible, yet difficult. As we shall demonstrate in Section 4, we can use profiling techniques, à la Hipster [44], to identify variations in program behavior. However, this approach has two shortcomings. First, distinct program parts, with very different resource demands in terms of memory, CPU, disk and such, can display similar dynamic characteristics. For instance, we could imagine a scenario in which function read user data, in Figure 1.2 is implemented via busy waiting. In this case, instead of the valleys observed in Figure 1.3, we would encounter a power line similar to that produced by CPUintensive functions like mulMatrix. Second, profiling-based techniques face a tradeoff between precision and overhead. Fast detection asks for high sampling rates; thus burdening the application which originally we intended to optimize. On the other hand, purely static approaches are not better either. Although likely to yield lower adaptation overhead, they fail to account for information only available at runtime such as varying input sizes. For instance, a static scheduler might decide always run mulMatrix and read user data in different configurations. However, when operating on matrices that are too small, the cost of changing the hardware configuration might already overshadow the possible gains available through more parsimonious usage of the architecture's resources.

**Figure 1.3.** (a) Power profile of program seen in Figure 1.2. The NI 6009 sample rate was 1000 samples/sec. (b) Zoom of the power profile obtained during the last phase of the program. We show power data obtained using one low-frequency core (Low), and using one ARM A15 core (High).

**The Search for the Ideal Architecture Configuration** In face of the data presented in this section, it comes as no surprise that the best architecture configuration, in terms of runtime or energy consumption, differs among programs.

Figure 1.4 shows the best configurations that we have found on the Odroid XU4 setup, for six different PARSEC applications. In this case, we define the best configuration as the one that spends less energy, given a certain slowdown compared to the fastest configuration. Clearly, there is not a single winner. Configurations vary among programs, and even within the same program, given different acceptable slowdowns.

**Saving Energy while maintaining Performance Constraints** Save energy while maintaining performance is a multi-dimensional optimization problem. Ideally, we want the maximum performance at the cost of the minimum of energy.

The multi-dimensional optimization is applied inside a program phase. This phase is usually defined by one of the two ways:

1. We fix a code section, regardless of the time it takes to execute. At the end of the code section, we analyze the process behavior inside it.

#### 1.2. Empirical Observation

Figure 1.4. Best configurations for seven PARSEC applications, given an acceptable slowdown of 1% or 5% compared to fastest configuration.

2. We fix a specific time interval, regardless of where the application is going to stop at the end. At the end of the time interval, we analyze the process behavior inside it.

Henceforth, we call a program phase defined by any of the approaches above as phase, section, region, application region or even a code section. Inside this region, a power usage metric could be, for example, Average Power or Peak Power spent in a code section or in a fixed interval. For the performance metrics, we could consider at least 3 approaches. First, the Elapsed Time (if we fix a code section). Second, estimating how much of the application is complete<sup>6</sup> (if we fix a time interval measurement). Third, use a throughput metric such as average instructions per second (what can be also application specific metrics such as a number of frames/seconds). We actually use the energy itself as a power consumption metric, even though it is quite clear that by considering energy as a metric we are already optimizing for performance also. Finally,

<sup>&</sup>lt;sup>6</sup>would require previous information of instructions in a previous run

for a given application region, we have two inputs, power related and a performancerelated metric and we want ideally maximize performance while minimizing power consumption.

**Energy-efficiency metrics** There exist plenty of metrics for the multi-dimensional problem approached in the context of hardware configuration. Before starting with multi-dimensional metrics, it is important to notice that getting one-dimensional only metric such as peak or average power, would be impractical metric for this kind of problem, as noticed by [51], a metric "should not reward a system that consumes almost no power and completes almost no work". We extend that, by stating that in the domain of embedded and mobile devices, a metric should not reward a system that does meaningful work but consumes an exorbitant amount of power, due to the battery restrictions. There are many approaches and metrics to handle this multi-dimensional problem in the literature. Some of them are:

- 1. Find a metric that combines both power and performance.

- 2. Minimizing or maximizing one of the dimensions and apply constraints on the other dimension.

Basic metrics that consider both dimensions are energy (product of time and power), and the energy-delay product. Furthermore, metrics such as Energy per instruction (*Joules/Instructions*) or *MIPS/watt* have being used by chip vendors [26]. Furthermore, tuning these formulas in the way such as  $MIPS^{alpha}/watt^{beta}$ , where *alpha* and *beta* tends balance performance and energy, have been used as well. Examples would be the  $MIPS^2/watt$  what relates to energy \* delay and  $MIPS^3/watt$  which is related to energy \* delay^2[33].

We have focused on approach (2). We minimize energy given some slack of performance degradation permitted. This is a more clear way to provide performance guarantees from the user perspective. In the domain of heterogeneous architectures especially in mobile devices and embedded architectures, we want to provide performance guarantees in an easier way while keeping the main goal of saving energy. The decision for the shape of a function that will balance these metrics for the system, can be found on 3.2.4.

**Heterogeneous multi-processors example** Regarding the understanding of opportunities in one of the Big.LITTLE setups, we have two different clusters, the A7 cluster and the A15 cluster combined inside the same chip. The so-called little cluster, A7, is designed for low load applications. The architecture is composed by processors in-order, with a dual issue, with one integer ALU and one partial ALU, one float point unit and pipeline stages varying from 8 to 10 stages depending on the instruction executed. The so-called Big cluster is more robust. In the setup A7-A15, it is composed of the A15 cores. Each of the A15 is an out-of-order processor, has a triple issue, two float point units, achieving a higher throughput on intensive loads. However, its pipeline stages vary from 15 to 24 stages depending on the executed instruction. As the number of pipeline stages usually leads to more energy consumption, the big cluster spends more energy than the little cluster. Furthermore, the low cluster frequency can be adjusted to work at a maximum of 1.4 GHz while the big cluster varies up to 2.3 GHz which also increases the energy spent.

**Core migration and DVFS** When handling heterogeneous processors as commented above, among the options of actions, we can deal with the dynamic voltage and frequency scaling (DVFS) as well as core migrations. A core migration over heterogeneous cores in a naive architecture could be unfeasible due to the cache incoherence between the cores. So, some heterogeneous architectures facilitate full-coherency between L2 caches of each one of the clusters (big and little cluster). In the Big.LITTLE architecture, it is done by the CCI-400 bus. Another motivation to do a core migration between two different type of cores in a big.LITTLE architecture is the small overhead. According to [24] it takes around 20.000 cycles, in a 1 GHz processor it would take 20 microseconds, in practice close to 30 micro-seconds what is lower comparing for example with a DVFS change that is expected in a few hundreds of microseconds. The big.LITTLE architectures also have some capabilities that motivate the migration between cores such as the possibility of migrating interruptions among the cores via the GIC-400 bus.

**Next chapters** In this chapter, we have highlighted key motivation behind our design: (i) a modern heterogeneous hardware exposes a number of different configurations that is too large to be evaluated manually; (ii) a program presents power phases, which can be more easily detected by methods that are aware of structural properties of the code. Thus, we claim that effective adaptation demands knowledge of program characteristics. Such information is readily available to the compiler; however, it is hard to be precisely acquired by techniques unaware of the program's structure. In the next chapters, we shall describe a few methodologies mixing static and dynamic analyses, to find good hardware configurations for the code sections invoked during the execution of a program. After a few evaluations, we end up with a general methodology, henceforth called the Astro system.

# Chapter 2

## Literature Review

In this chapter we explain and survey the main techniques used nowadays to execute code in heterogeneous architectures. The goal of this section is to give the reader enough context to understand the benefits and limitations of the Astro framework.

### 2.1 Handling the Code Placement Problem

#### 2.1.1 The Static solution: decision at compiling time

A purely static solution retrieves information from the code and based on their values, maps phases of the code to processor units. Examples of that is Etino [48]. A summary of static characteristics are:

- Source code available, source of predictions

- If code section is executed with periodicity, it can use history to predict.

- No need of monitoring execution

- Changes on types of workloads can lead to very bad allocation mistakes, leading to over requiring or minimizing actual need. Impacts direct on cost.

- We can instrument the placement in the binary already, so no need for a middleware manage the changes of workload.

In the table bellow, there are some static features used in our solution. Features 1-4 are from [25]. They are a subset of the original set of features presented in the dissertation. The features are retrieved for each function (as a function is our learning unit) instead of for a full program in its original propose. Furthermore, we collect via a static pass in the LLVM compiling framework. Some features were not selected as they were strongly related with GPUs which are not our target architectures. Features 10-16 and 19-23 are a subset of the features present on [3] extended with a few features

for functions instead of each loop.

| $3 \qquad \# \text{ int operations (estimative)}$          |                |

|------------------------------------------------------------|----------------|

|                                                            |                |

| $4 \qquad \qquad \# \text{ float operations (estimative)}$ |                |

| 5 is this code section right before a sleep lib            | call? (flag)   |

| 6 is this code section right before a network like         | o call? (flag) |

| 7 $\#$ locks (estimative)                                  |                |

| 8 is this code section right before a sync. bar            | rier? (flag)   |

| 9 $\#$ total of instructions (estimative                   | e)             |

| 10 $\#$ branch instructions within funct                   | ion            |

| 11 max loop step within function                           |                |

| 12 max loop nest depth within function                     | on             |

| 13 $\#$ math lib calls (estimative)                        |                |

| 14 contains loops? (flag)                                  |                |

| 15 loops perfectly nested (flag)                           |                |

| 16 any loop has calls (flag)                               |                |

| 17 any loop has branches? (flag)                           |                |

| 18 contains nested loops (flag)                            |                |

| 19 all loops have constant lower bound?                    | (flag)         |

| 20 all loops have constant upper bound?                    | (flag)         |

| 21 all for loops have constant stride? (f                  | lag)           |

| 22 all for loop have unit stride? (flag                    | <u>(</u> )     |

| 23 all loops are simple within function                    | on             |

| 24 is this an internal OpenMP function                     | call?          |

|                                                            |                |

Someone can use these raw features, as in the table, or compose one or more of them to create new features such as: normalized int operations per total of instructions.

| # | Dynamic envir features (per core) |

|---|-----------------------------------|

| 1 | CPU utilization                   |

| 2 | Number of instructions executed   |

| 3 | Number of last level cache misses |

| 4 | Number of branch miss-predictions |

| 5 | Number of cache accesses          |

| 7 | Number of memory reads            |

| 8 | Number of memory writes           |

|   |                                   |

#### 2.1.2 The Dynamic solution: decision at running time

A purely dynamic solution retrieves information from the workload, hardware and the process. Someone can use these raw features, as in the table, or compose one or more of them to create new features such as: Instructions per cycle (IPC), Cache Miss Ratio (CM ratio) or Cache Miss rate (CM rate). Based on it, maps phases of the code to processor units. Examples of that are Hipster ([44]) and OctopusMan ([46]). We suggest a simple table with the dynamic features used in our solution.

Dynamic characteristics:

- No code, so no prediction based on it.

- Accurate decisions based on real time analysis of the hardware and processes.

- If workload has periodicity, it can use history to predict.

- Usually have showed good results, but with the cost of monitoring execution

#### 2.1.3 Hybrid Motivation: Static vs Dynamic decisions

We want to motivate that dynamic and static features are complementary and both of them are necessary for our solution. Consider the following C where we need to set two architectures, before "mult" and before "out":

```

int main() {

1

N = 100;

2

in(X,N); in(A,N); in(B,N); // initialize matrices of size NxN

3

setArchitecture(?) // (1)

4

mult(X,A,B,N); // Does X=A*B; "*" is matrix multiplication op.

5

setArchitecture(?) // (2)

6

out(X,N); // Outputs the X matrix of size NxN

7

free(X);free(A);free(B);

8

return 0;

9

```

10 }

In the question marks at (1) and (2) we are asked to choose between "LOW CORE", "HIGH CORE", to pass to the argument, representing respectively a code placement for an architecture of mult and out functions. The "LOW CORE" denotes a configuration towards low power consumption exploitation. The "HIGH CORE" denotes a configuration with high performance capabilities. What would be a reasonable choice? We start by stating that the best choice in terms of total energy would be: (1) "LOW CORE" and for (2) also "LOW CORE", making it as the following:

```

// Known best choice: Optimal Solution

1

int main() {

\mathbf{2}

//...

3

setArchitecture("LOW CORE") // (1)

4

mult(X,A,B,N);

5

setArchitecture("LOW CORE") // (2)

6

out(X,N);

7

// ...

8

9

}

```

We could choose for take into account only static information first, i.e. the static approach only, the approach considering the static code features presented. We probably would set the matrix multiplication to HIGH CORE core and the output to the LOW CORE core.  $^1$

```

// Static only decision

1

\mathbf{2}

int main() {

11 . . .

3

setArchitecture("HIGH CORE") // (1)

4

mult(X,A,B,N);

5

setArchitecture("LOW CORE") // (2)

\mathbf{6}

out(X,N);

7

// ...

8

9

}

```

<sup>&</sup>lt;sup>1</sup>For the code mentioned, an action based in a static analysis that could see more than its own function information would probably go to the optimal solution. For example, for this example, a simple constant propagation (a compiler optimization) plus computing the estimated number of instructions via static inference might easily solve it. However, keep in mind the N=100 in the source code is an oversimplification. The same input could be harder to retrieve from source code or even run-time based. So, we argue that the static choice would still be valid for one of the two: N=100 in the source code, but a simple static analysis just looking at the function level (our example); or a fancy static analysis but with input information that is hard to retrieve or run-time based.

#### 2.1. HANDLING THE CODE PLACEMENT PROBLEM

However, the input size is 100x100 and the actual best fit (by now only looking in terms of most energy savings), both of them should run in the low-core.

Following a only dynamic approach: we could use a perf command, see the cpu usage of multiplication, as it is low, we set (1) to "LOW POWER". Then, as out start to execute, we see that the resource usage is even lower, so, no necessity to turn on the big core we set as "LOW POWER". So, it would answer it right. However, first, the signal of low usage can not be very precise when monitoring this part of the code, there is a delay of our action and state that the profiler is showing us, more than that, besides that, we become dependent to monitor the execution the whole time. Using the static to predict this phase, we could make this decision ahead of time, becoming more independent of the dynamic part, a great IO density in the next function is a strong indicative (signal) that we shold use less processing. Even though the runtime overhead on dynamic approaches can be sometimes (as in [44]) negligible for servers, when we deal with embedded architectures and energy concerns, this overhead is not negligible.

#### 2.1.4 The Hybrid: combining Dynamic and Static information

An hybrid code placement solution is a method which combines both information (source code and dynamic reads) in the placement decision problem. It tries to couple these two worlds helping placement on heterogeneous architectures. A proposed hybrid code would work as following:

- 1. Component 1: initial instrumentation

- a) Instrument a source code A such as compute all static features of code phases (for simplicity, assume every function) and mark at run time which phase is running, generating a binary B.

- b) During B running time you should be able to know which phase is running and know its static features (characteristics) values.

- 2. Component 2: learning (during execution of B)

- a) Define a sampling interval which you will collect dynamic features and the function which is running.

- b) Make a decision (according to a learning model) about which hardware configuration changes.

- c) Act in the system changing to the decided configuration.

- d) Collect performance measures such as Energy and Performance in order to evaluate the action made.

- 3. Component 3: final instrumentation

- a) In the final of the learning, you will have actions for every sampling interval (decision point) and consequently to the function that were running at that interval.

- b) See which are the actions made for every phase and decide which ones remains.

- c) Take A and generate a new binary B on each phase with hardware adjusts instruction commands.

|                                | Static                                                                                                                                                                                 | Dynamic                                                                                                                                                                               | Hybrid                                                                                                                                                                    |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Scheduling respon-<br>sibility | Compiler                                                                                                                                                                               | Operating system<br>or Middleware                                                                                                                                                     | Both                                                                                                                                                                      |

| Advantages                     | Can use structure<br>of the program to<br>take better deci-<br>sions; If the code is<br>executed with peri-<br>odicity, it can use<br>history to predict;<br>No run-time over-<br>head | Possibility to use<br>run-time informa-<br>tion to improve the<br>quality of choices;<br>If the workload is<br>executed with peri-<br>odicity, it can use<br>history to predict       | Best of both<br>worlds: runtime<br>information for<br>accurate decision<br>and reduction<br>of overhead due<br>to predictable<br>program character-<br>istics             |

| Disadvantages                  | Same program can<br>work completely<br>different on, for<br>example, different<br>input sizes; Some-<br>times we do not<br>know which parts<br>of the code are<br>going to run         | High overhead<br>from the runtime<br>monitoring; Some-<br>times, not clear<br>understanding<br>of the program<br>behavior, causing<br>sometimes pre-<br>dictions not very<br>reliable | The two sources<br>of overhead: run-<br>time monitor<br>overhead plus the<br>instrumentation.<br>Requires a careful<br>combination of<br>static and dynamic<br>decisions. |

### 2.1.5 Trade-offs

| Work  | Level          | Source | Auto | Runtime | Learn |

|-------|----------------|--------|------|---------|-------|

| [48]  | С              | Yes    | Yes  | No      | Yes   |

| [43]  | L              | No     | Yes  | Yes     | Yes   |

| [17]  | $\mathbf{C}$   | Yes    | Yes  | No      | Yes   |

| [6]   | $\mathbf{C}$   | Yes    | Yes  | Yes     | No    |

| [52]  | $\rm C/L$      | Yes    | No   | Yes     | No    |

| [36]  | $\mathrm{C/L}$ | Yes    | No   | Yes     | No    |

| [30]  | A/L            | Yes    | No   | No      | No    |

| [37]  | А              | No     | Yes  | No      | No    |

| [56]  | А              | No     | Yes  | No      | No    |

| [44]  | Ο              | No     | Yes  | Yes     | Yes   |

| [46]  | Ο              | No     | Yes  | Yes     | No    |

| [19]  | Ο              | No     | Yes  | Yes     | Yes   |

| [5]   | $\mathbf{L}$   | Yes    | No   | No      | No    |

| [47]  | O/C            | Yes    | Yes  | Yes     | No    |

| [55]  | O/C            | Yes    | Yes  | Yes     | No    |

| [16]  | O/C            | Yes    | Yes  | Yes     | No    |

| Astro | O/C            | Yes    | Yes  | Yes     | Yes   |

**Table 2.1.** Comparison between different solutions to . *Level*: at which level the technique is implemented: Architecture (A), Operating System (O), Compiler (C) or Library/Programming model (L). *Code*: "Yes" if there is source code instrumentation/manipulation. *Auto*: "Yes" if it is performed automatically, without user intervention/annotation. *Runtime*: "Yes" if technique considers runtime information. *Learn*: "Yes" if technique adapts/learns a model from the target architecture

### 2.2 Non-assisted code-placement

The problem of scheduling computations in heterogeneous architectures (Definition 3.0.1) has attracted much attention in recent years, as Mittal and Vetter have thoroughly discussed [40]. Table 2.1 provides a taxonomy of previous solutions to this problem. We group them according to the level (e.g., ../..) at which they are implemented, and to the way they answer each of the following four questions:

Source: is the program's code modified?

Auto: is user intervention required?

Runtime: is runtime information exploited?

**Learn**: is there any adaptation to runtime conditions? Perhaps the most important difference among the several strategies proposed to solve concerns the moment at which said strategy is used. In the rest of this section, we consider the following three possible choices: at compilation time, at runtime, or both.

Static Solutions. Purely static approaches work at compilation time. They might be applied by the compiler, either automatically, i.e., without user intervention [16; 29; 36; 52; 48; 55], or not. In the latter case, users can use annotations [39], domain specific programming languages [36; 52] or library calls [5] to indicate where each program part should run. The main benefit of static techniques is low runtime overhead: because every scheduling decision is taken before the program runs, no dynamic checks are necessary to schedule computations. However, these techniques tend to be inflexible: they are unable to take runtime information into consideration; hence, the same program phase is always scheduled in the same way. In Table 2.1, techniques implemented at either the compiler or library levels are purely static.

**Dynamic Solutions.** Purely dynamic approaches take into account runtime information. They can be implemented at the architecture level [50; 37; 30; 56; 60], or at the virtual machine (VM)/OS level [46; 44; 63; 21; 53; 6]. By leveraging runtime information, the system can use environment information, unknown at compilation time, to solve . Examples of such information include varying input sizes and resource demands. However, there may be some overhead on accurately collecting and processing runtime data. Besides, because scheduling decisions are taken on-the-fly, usually the scheduler cannot spend much time weighting choices. Thus, even though these algorithms use runtime information, they might still take suboptimal decisions, due to their inability to spend much time solving hard scheduling problems.

**Hybrid Solutions.** Approaches that mix static and dynamic techniques are called *hybrid.* Astro is a hybrid method, and built around the idea of being a customized framework for other hybrid methods. Other hybrid approaches to this problem exist [47; 16; 55]. Piccoli *et al* [47] have used a compiler to instrument a program with guards that determine, based on input sizes, where each loop should run. Cong and Yuan [16], in turn, partition a program in phases, as in our approach, and use runtime information to schedule computation so as to minimize the energy consumed by the program. Finally, Tang *et al.* [55] use a compiler to populate a program code with markers, so that low-priority applications can manage their own contentiousness to ensure the QoS of high-priority co-runners. None of these previous work use any form of learning technique to adapt the program to runtime conditions, as Table 2.1 indicates in the column *Learn.* Once guards are created, they always behave on the same way. That is the main difference between these previous approaches and the Astro method.

# Chapter 3

# Astro framework

This chapter describes the design and implementation of the Compile assisted Adaptive Code Placement in Heterogeneous Systems, called Astro Framework. This is our approach to solve the problem of finding good hardware configurations for programs. We state this problem as follows:

**Definition 3.0.1** Scheduling of Programs in Heterogeneous Architectures (SPha)

**Input**: a program P plus its input I, a suite of hardware configurations  $H_1, H_2, \ldots, H_n$ , an energy threshold E, and a performance threshold S.

**Output**: P', a new version of P, which switches between configurations, and process I using E% less energy, with a slowdown of no more than S%.

We solve SPHA using an assortment of different techniques, which, once combined, give us the means to generate code that is well adapted to different architectures and workloads. Figure 3.1 provides a general overview of these techniques, emphasizing the different phases over which we go in the process of solving SPHA. Section 3.2.1 describes the phase partitioning. Program instrumentation is necessary to the program partitioning phase. Section 3.2.2 goes over actuation; and Section 3.2.3 discusses the generation of the final program. Before we move into the particulars of our solution to SPHA, we provide a brief introduction to Q-Learning, the flavour of reinforcement learning that we have adopted. In the next section, we also explain how we map the characteristics of SPHA into the Q-learning framework. Before we came up with this approach, we have tested others. For instance, we Supervised Learning solutions in a simplified problem, as seen in Section 4.0.2.1.

### 3.1 Reinforcement learning via Q-Learning

Q-learning is a reinforcement learning algorithm [54]. Given some notion of state (Definition 3.2.1) and reward (Definition 3.2.4), it finds an optimized policy to perform the best action (Definition 3.2.5). Q-learning is attractive because there is no need to know in advance the precise results of the actions before we perform them; that is, we learn about the environment as we perform actions on it. A Markov Decision Process (MDP) drives Q-learning. A MDP is given by a set of states S, a set of possible actions A, a reward function  $R: S \times A \to R$ , and a state transition mapping  $T: S \times A \to S$  that describes the effects of taking each action in each state of the environment. The Markov property states that the results of an action performed in a state will depend only on that particular state, regardless of any other prior states.

In Q-learning, the function Q(s, a) is specified to tell us how good an action a is given that we are in a certain state s. Intuitively, it approximates the best possible sum of rewards from s till the final state, assuming that we perform always optimal choices. Predicting optimal choices from any given state is usually impossible; thus,

Figure 3.1. The Astro Framework.

we approximate Q with the Bellman Equation:

$$Q_{target}(s, a) = R(s, a) + \gamma \operatorname{argmax}_{a'}(Q(s', a')).$$

Here, s' is the state that follows from the application of action a onto s, and a' is the best possible action taken from s'. R(s, a) is the immediate reward computed from the environment. Value  $\gamma \in [0, 1]$  represents a balance between prior and immediate reward. At each step in the Q-learning algorithm, we choose the action a that maximizes the function Q(s, a).

Traditionally, the Q-learning algorithm uses a tabular form to represent the Q(s, a) mappings, but this approach cannot scale and generalize well to high dimensional feature spaces. Similarly to recent prior work on reinforcement learning [41], we use a neural network to approximate the Q(s, a) function used to compute the expected reward from a given state s and action a.

To find a good approximation of Q(s, a), we use a neural network (NN), to track its current value. Thus, "learning" means actually updating the NN. At each iteration of our learning process, we update the NN using Stochastic Gradient Descent (SGD) [10] over the squared error over the target values (via Bellman equation) and the values obtained by our network:

$$\sum (Q_{target} - Q)^2.$$

#### 3.1.0.1 Motivation for the model used

Motivation to a reinforcement learning model When building a supervised solution for an application in the PARSEC benchmark such as fluidanimate, we took roughly a whole day of execution. We could retrieve the labels for its phases by exhaustively executing the application in the 24 different possible combinations of big and little cores in the ARM Big.LITTLE board. Increasing this action allowing five frequency changes for every configuration in a DVFS setup, we would have  $24^5 = 7,962,624$ configurations to evaluate. Furthermore, we are assuming that the placement for one phase does not affect the other, what is not true. Therefore, if we expand the problem space or break the assumption of phases don't affect each other or even consider a multiple application scenario, it is clear unfeasible to work with the traditional supervised learning approach. We could try to work around this problem trying to restrict our space as [43], keep the assumptions, and maybe use heuristics to extrapolate from a learned space to the actual problem space, but we have recognized that reinforcement learning solution fits to the problem more naturally. **Influences to the model used** The prediction model design (definition of state, action and reward function) of Astro was based on three main approaches. They are [18], [31], [61] and [57].

The [18] handles a thermal optimization, it has a multi-objective function which tries to reduces the thermal dissipation and maximize performance. On [31], has a similar problem which solves via reinforcement learning and considers temperature and performance as a multi-objective reward function. However, its solution is based in the manipulation of idle periods, not our focus. Some ideas, such as the combination of multi-objective functions in a reward function, and the shape of the function (with a restriction applied to the function as a subtraction to the original value) came from these articles. Other than these three main articles, [57] uses reinforcement learning and has a dynamic approach trying to formalize the problem of allocating (and migrating) resources in a heterogeneous multi-core architecture. The reward function is given in terms of the CPU and memory usage. The reward function is a single-objective, trying to reduce only the waiting time.

Related to reinforcement learning using neural networks, it had a great impact on [41]. In this article, neural networks extends the use of a q-table on their solution. However, the problem and the motivation for the use of a neural network are different. In the problem approached by the article, there is a inherent representational complexity in the problem (they did not know, without simplifying too much, how to model the states of the games). A state, thus, was represented as images of the game, while in this dissertation we assume we know how to represent our environment given the dynamic and static characteristics we have chosen. Other than that, the article presents an agent that could play several the games well aiming an agent which can play well a class of problems really well. In our case, we specify a single problem, the code placement on heterogeneous architectures minimizing energy with performance restrictions.

### 3.2 Components of the Astro framework

### 3.2.1 Part 1: Phase Partitioning

A running program might cause the hardware to go over an infinite number of different states. Because this universe is unbounded, Definition 3.2.1 discretizes the notion of a *State*. In that definition, S is a *Program Phase* and D is a *Hardware Phase*. Program phases are discussed in Section 3.2.1.1, and hardware phases are discussed in Section 3.2.1.2.

#### 3.2. Components of the Astro framework

**Definition 3.2.1 (State)** A state is a triple  $\langle H, S, D \rangle$  representing a hardware configuration H, a program phase S and a hardware phase D.

#### 3.2.1.1 Program Phases

Static Program Phases depend only on the syntax of a program. Definition 3.2.2 formalizes this notion. We emphasize that a static program phase is not equivalent to a *program region*, because different regions can present the same set of feature ranges. Example 3.2.1.1 clarifies the meaning of these definitions.

**Definition 3.2.2 (Program Phase)** A code-level feature (also called code feature or simply feature) is a syntactic characteristic of a program, such as number of n-nested loops or instruction mix. A feature range is a contiguous interval of values that a feature can assume, and that partitions the feature space into equivalence classes. A program phase S is a group of feature ranges, covering different features.

The density of arithmetic and logical instructions is a code-level feature, which we obtain by dividing the number of such opcodes by the total number of program instructions. We can define different feature ranges covering this metric, such as [0, 0.25), [0.25, 0.50) and [0.5, 1.00]. The highest number of nested loops in a program yields another feature. In this case, possible ranges are [0, 1], [2, 3] and  $[4, +\infty]$ . Finally, an expectation on the number of I/O routines called in a function gives us a third feature. A possible way to calculate it is:  $\Sigma_i 10^n$ , for every I/O call *i* nested into *n* loops. We can, again, define intervals for this metric, e.g., [0, 1), [1, 10) and [10, 100) and  $[100, +\infty]$ . The  $3 \times 3 \times 4$  possible combinations of such feature ranges gives us 36 program phases. If we collect these features for each function in the program code, then we can map any of them to one of these program phases.

Being a syntactic characteristic of a region within a program text, we can mine program phases using well known parsing techniques. The text that ends up executed is the binary representation of a program, often written in a high-level language. Thus, ideally parsing should be performed in that binary representation. Recovering highlevel structure from binary programs involves a number of undecidable problems [27]. To circumvent this shortcoming, we recommend mining features from the intermediate program representation that the compiler manipulates before producing executable code. In this work, we have implemented a *Phase-Extractor* using the LLVM compiler, via its opt bytecode analyzer.

The result of mining program features is a map that assigns phases to program regions. This map depends on the choice of program region. Many different granularities

Figure 3.2. Mapping the functions in Figure 1.2 (a) to program phases.

of regions are possible, such as instruction, basic block, loop, Single-Entry-Single-Exit block [20], etc. We have chosen to work mostly at the granularity of functions. The "mostly" in this case, refers to the fact that we also change phases before and after library calls that cause the program to block waiting for some event (see the **Barrier** phase, in the discussion that follows). Pragmatically, this means that the instrumented program adds logic to change phases at the entry point of functions, and around certain library calls.

Figure 3.2 shows the five functions in Figure 1.2, classified according to features seen in Example 3.2.1.1. We are assigning these functions hypothetical values. Because we have three features, we can map them into a three-dimensional space. Each phase corresponds to a cube in this space. Figure 3.2 shows the sub-space that corresponds to the phase: Arith.Density  $\in [0, 0.25)$ , I/O Weight  $\in [0, 1)$  and NestingFactor  $\in [0, 1)$ . Function main, in our example, fits in this phase.

**Discrete Choice of Program Phases.** In our discrete implementation, we combine four code features to determine program phases. These features are all "densities", i.e., they represent a certain quantity of instructions normalized by the total of instructions

#### 3.2. Components of the Astro framework

in the target function. The features that we have used are listed below:

**IO-Dens**: proportion of library calls that perform I/O operations;

Mem-Dens: proportion of instructions that access memory (loads and stores);

Int-Dens: proportion of arithmetic and logic instructions that operate on integer types.

**FP-Dens**: proportion of arithmetic and logic instructions that operate on floating point types.

Locks-Dens: proportion of lock instructions.

Barrier: true if the program has invoked a multi-thread barrier library call that forces it to wait for some blocking event.

Network: true if the program has invoked a networking library call that forces it to wait.

Sleep: true if the program has invoked a sleep library call that forces it to wait.

When handling with our discrete variables, we have defined four program phases, which appear as combinations of the features above. This choice is arbitrary. There exists an infinite number of different possibilities to partition programs in phases. We have opted for a simple partitioning, involving only a handful of features for convenience, as this choice already lets us support the main thesis of this dissertation: that static features greatly enhance the dynamic scheduling of computations in heterogeneous hardware. A more extensive search for good program phases is, in itself, an interesting project, but lays outside the scope of this work. The program phases that we shall consider in the experiments using the simulator in Section 4 are:

Sync: Barrier = true or Sleep = true or Network = true or Locks/total > 0.01

I/O Bound: IO-Dens + Mem-Dens > 0.5and Sync = false;

CPU Bound: Int-Dens + FP-Dens > 0.5and Sync = false and I/O Bound = false

Other: in case none of the previous relations hold.

**Continuous Choice of Program Phases.** When using a deep reinforcement learning, each static feature collected corresponds to a neuron in the input layer. For the main our experiment, on Table 4.1, we use this continuous approach with no combination of variables.

#### 3.2.1.2 Hardware Phases

Whereas the program phases seen in Section 3.2.1.1 depend only on syntactic program characteristics, *hardware phases* depend on the dynamic state of the hardware. We define the notion of hardware phase as follows:

**Definition 3.2.3 (Hardware Phase)** A Performance Counter is any monitor that collects dynamic information about the hardware state, such as CPU performance and cache miss rate. The domain over which the performance counter ranges can be partitioned into phases. Given a collection of performance counters  $\{C_1, C_2, \ldots, C_n\}$ , where each  $C_i$  is partitioned into  $R_i$  phases, then a hardware phase is any combination within the product  $R_1 \times R_2 \times \ldots \times R_n$ .

The monitoring of hardware phases do not require program instrumentation. Instead, an *actuator* reads the state of the hardware performance counters directly and periodically. Modern computer architectures already provide an array of performance counters that can be queried. When such is not the case, it is still possible to approximate hardware phases in software. As an example, Walker *et al.* [59] describe how to estimate current levels of power dissipation with high reliability using performance counters.

**Discrete Choice of Hardware Phases.** We consider four kinds of dynamic information in order to define hardware phases. We show, next to each dynamic feature its discretization into ranges we used in our initial experiments:

IPC: instructions per cycle in the ranges  $[0, .5), [.5, 1.0), [1.0, +\infty);$

CMA: cache misses per cache accesses in the ranges  $[0, 1\%), [1\%, 5\%), [5\%, +\infty);$

CMI: cache misses per instruction executed, in the ranges  $[0, .1\%), [.1\%, .5\%), [.5\%, +\infty);$

CPU: utilization of the CPU, in the ranges [0, 20%), [20%, 50%),  $[50\%, +\infty)$ . Each of these counters is partitioned in three buckets. Therefore, we consider a total of  $3 \times 3 \times 3 \times 3 = 81$  different hardware phases.

**Continuous Choice of Hardware Phases.** The continuous consider as hardware phases the hardware features plus one feature being the configuration which the hardware (dynamic) features were collected. When using a deep reinforcement learning, each hardware feature corresponds to a neuron in the input layer.

#### 3.2. Components of the Astro framework

Figure 3.3. The Actuation Algorithm.

#### 3.2.2 Part 2: Actuation

The heart of the Astro system is the Actuation Algorithm outlined in Figure 3.3. Actuation consists of *phase monitoring*, *learning* and *adaptation*. These three steps happens at regular intervals, called *check points*, which, in Figure 3.3, we denote by i and i+1. The rest of this section describes these events.

#### 3.2.2.1 Monitoring

To collect information that will be later used to solve SPHA, Astro reads four kinds of data. Figure 3.3 highlights this data: