# UNIVERSIDADE FEDERAL DE MINAS GERAIS INSTITUTO DE CIÊNCIAS EXATAS DEPARTAMENTO DE CIÊNCIA DA COMPUTAÇÃO

# TOLERÂNCIA A FALHAS ATRAVÉS DE ESCALONAMENTO EM UM SISTEMA MULTIPROCESSADO

# MARCOS PÊGO DE OLIVEIRA

**BELO HORIZONTE BRASIL**

**FEVEREIRO 2004**

## MARCOS PÊGO DE OLIVEIRA

# TOLERÂNCIA A FALHAS ATRAVÉS DE ESCALONAMENTO EM UM SISTEMA MULTIPROCESSADO

Tese de Doutorado submetida ao Curso de Ciência da Computação do Instituto de Ciências Exatas da Universidade Federal de Minas Gerais, como requerimento parcial para a obtenção do grau de Doutor em Ciência da Computação.

Orientador : ANTÔNIO OTÁVIO FERNANDES Co-Orientador: SÉRGIO VALE AGUIAR CAMPOS

## **BELO HORIZONTE BRASIL**

## **FEVEREIRO 2004**

UNIVERSIDADE FEDERAL DE MINAS GERAIS

## FOLHA DE APROVAÇÃO

## Tolerância a Falhas Através de Escalonamento em um Sistema Multiprocessado

## MARCOS PÊGO DE OLIVEIRA

Tese defendida e aprovada pela banca examinadora constituída pelos Senhores:

Prof. ANTÔNIO OTÁVIO FERNANDES - Orientador Departamento de Ciência da Computação - UFMG

Prof. SÉRGIO VALE AGUIAR CAMPOS - Co-orientador Departamento de Ciência da Computação - UFMG

TOT. TOTATOA SILVA FR

Departamento de Engenharia Elétrica - UFSC

Prof. LUIGI CARRO Departamento Engenharia Elétrica - UFRGS

Prof. PORFÍRIO CABALEIRO CORTIZO Departamento de Engenharia Eletrônica - UFMG

Prof. CLAUDIONOR JOSÉ NUNES COELHO JÚNIOR Departamento de Ciência da Computação - UFMG

Belo Horizonte, 27 de fevereiro de 2004.

# Agradecimentos

À Adriana, Bárbara, Débora e Pâmela, minha esposa e filhas, pelo pleno apoio durante todo o desenvolvimento deste trabalho.

Aos meus pais, pela sólida educação que sempre me permitiu enfrentar os mais difíceis desafios com muita firmeza e tranqüilidade.

Ao Aluísio, meu irmão, que me apoiou e conduziu a Engetron durante os momentos que dediquei ao curso de Doutorado.

Aos professores Antônio Otávio e Sérgio Campos, pela orientação, confiança em meu trabalho e constante incentivo.

Aos professores Edmund Clarke e Raj Rajkumar pela orientação durante o período de 1 ano que estive na Carnegie Mellon University como cientista visitante.

À Ana Luiza Zuquim, pelo trabalho que desenvolvemos juntos, fazendo análise crítica dos resultados, editando e corrigindo diversos textos de artigos e da tese.

À excelente equipe do Departamento de Ciência da Computação da Universidade Federal de Minas Gerais, pelo ótimo ambiente de trabalho e incontáveis contribuições para o desenvolvimento da minha linha de pesquisa.

# Acknowledgments

First and foremost I would like to thank Adriana, Bárbara, Débora e Pâmela, my wife and daughters, for the full support during the development of the whole work.

I am very greatful to my parents, for the solid education which prepared me to face chalenges firmly and serene.

I would also like to thank Aluísio, my brother, for his support and for managing Engetron while I was dedicating my time to my Doctorate course.

Special thanks are due to professors Antônio Otávio and Sérgio Campos, for their guidance, enthusiasm, and trust on my work.

I wish to thank professors Edmund Clarke and Raj Rajkumar for giving me directions on my work during the one year I've been at Carnegie Mellon University as a visiting scientist.

I would like to thank Ana Luiza Zuquim, for the work we developed together and for her assistance on writing several papers and the thesis.

I would especially like to thank everyone at the Computer Science Department of the Federal University of Minas Gerais, which provided me a great workplace and uncountable contributions to the development of my research.

## Resumo

Os requisitos de tolerância a falhas devem ser incluídos no projeto inicial de sistemas de tempo real, contemplando a integração de software, hardware e restrições de tempo. Existem muitos casos em que o projeto de tolerância a falhas deve ser incluído estaticamente, devido às altas taxas de dados e severas restrições de tempo. Sistemas que exigem alta segurança necessitam de técnicas formais de prova para garantir que os requisitos de tolerância a falhas serão cumpridos. Novas abordagens onde os sistemas podem prever que as restrições de tempo serão violadas permitem que decisões sejam tomadas antes que uma pane ocorra. Priorizar tarefas em sistema de tempo real é um problema pertencente à classe NP-Hard.

Várias alternativas para resolver este problema já foram propostas. Neste trabalho, investiga-se a possibilidade de se obter um nível mais alto de tolerância à falhas com a integração de alguns trabalhos correlatos. Este trabalho apresenta técnicas para melhorar a capacidade de tolerância a falhas de sistemas de tempo real incorporando redundância de tempo, redundância de processadores e protocolos de comunicação em tempo real e tolerantes a falhas. A principal meta é garantir os requisitos de tolerância a falhas para sistemas de tempo real multiprocessados. As ferramentas utilizadas para otimizar estes requisitos de tolerância a falhas são a escalonabilidade de tarefas e a redundância de tempo.

Este trabalho, em complemento a uma abordagem teórica, foi desenvolvido utilizando uma implementação composta de um sistema multiprocessado com CPUs DSP interconectadas por um barramento CAN. A pesquisa leva em consideração o overhead introduzido pelo protocolo de comunicação de tempo real tolerante a falhas.

# Abstract

Fault tolerance must be included in the initial design of real time systems, must encompass hardware and software, and must be integrated with timing constraints. In many situations, the fault-tolerant design must be static, due to extremely high data rates and severe timing constraints. Ultrareliable systems need to employ proof-of-correctness techniques to ensure fault tolerance properties. We also see new approaches where the system predicts that timing constraints will be missed, enabling early action on such faults. Prioritizing tasks in Hard-Real-Time Systems is a problem belonging to NP-hard class.

Various alternatives for solving that problem have already been proposed. In the present study, we have investigated the possibility of obtaining a high level of fault-tolerance with the integration of some works proposals. This work presents techniques to enhance the fault-tolerance capability of hard real-time systems by incorporating time redundancy, processor redundancy and fault tolerant real-time communication protocols. The main goal is to guarantee fault-tolerance requisites for multiprocessor hard real-time systems. The resources used to optimize these fault-tolerance tolerance requisites are task schedulability and time redundancy.

This work, aside from theoretical concerns, will research the implementation of using a DSP multiprocessor system interconnected by a CAN bus. The research will consider the overhead introduced by the real-time fault tolerant communication protocol.

# Contents

| AGRADECIMENTOSIII                                                    | l |

|----------------------------------------------------------------------|---|

| ACKNOWLEDGMENTS IV                                                   | 7 |

| RESUMO V                                                             | 7 |

| ABSTRACT                                                             | [ |

| LIST OF FIGURES                                                      | 1 |

| LIST OF TABLES                                                       | 2 |

| GLOSSARY                                                             | 3 |

| RESUMO EM PORTUGUÊS                                                  |   |

| Introdução                                                           | , |

| TRABALHOS RELACIONADOS                                               |   |

| Teoria Rate-monotonic                                                |   |

| Rate-monotonic e tolerância a falhas                                 |   |

| Protocolos de comunicação de tempo real tolerantes à falhas          |   |

| ABORDAGEM PROPOSTA E DESENVOLVIMENTO DO TRABALHO                     |   |

| Análise do tempo de transmissão de mensagens no barramento CAN       |   |

| Aplicando conceitos de tolerância à falhas ao protocolo CAN          |   |

| Limitação da taxa máxima de transferência por nó no barramento CAN   |   |

| Comparação de protocolos de tempo real tolerantes à falhas           |   |

| Estudo de caso – Utilização do RMCAN em um sistema de alimentação de |   |

| ENERGIA SEM INTERRUPÇÕES                                             |   |

| Conclusões                                                           |   |

| CHAPTER 1                                                            | 3 |

| INTRODUCTION                                                         | 3 |

| 1.1 OVERVIEW AND MOTIVATION                                          |   |

| 1.2 Thesis Goals                                                     |   |

| 1.3 Related Work                                                     |   |

| 1.4 Contributions                                                    |   |

| 1.4.1 Publications and other contributions                |          |

|-----------------------------------------------------------|----------|

| 1.5 ORGANIZATION                                          |          |

| CHAPTER 2                                                 |          |

| FAULT TOLERANCE IN REAL-TIME SYSTEMS                      |          |

| 2.1 OVERVIEW                                              |          |

| 2.2 REAL-TIME SYSTEMS                                     |          |

| 2.3 FAULT TOLERANCE                                       |          |

| 2.4 HARDWARE REDUNDANCY                                   |          |

| 2.4.1 Watchdog Timer                                      |          |

| 2.5 Software redundancy                                   |          |

| 2.6 INFORMATION REDUNDANCY                                |          |

| 2.7 TIME REDUNDANCY                                       |          |

| 2.8 GOALS OF FAULT TOLERANCE PROJECTS                     |          |

| CHAPTER 3                                                 | 51       |

| REAL-TIME FAULT TOLERANCE SCHEDULING                      | 51       |

| 3.1 Overview                                              |          |

| 3.2 RATE MONOTONIC THEORY                                 |          |

| 3.3 FAULT TOLERANCE AND RATE MONOTONIC SCHEDULING         | G 56     |

| 3.4 MULTIPROCESSOR SYSTEMS                                |          |

| 3.4.1 Fault tolerance in multiprocessor real-time systems |          |

| CHAPTER 4                                                 | 64       |

| REAL-TIME FAULT-TOLERANT COMMUNICATION PROT               | FOCOLS64 |

| 4.1 Overview                                              |          |

| 4.2 MEDIUM ACCESS PROTOCOL CLASSES                        |          |

| 4.3 MODEL FOR HARD REAL-TIME COMMUNICATION                |          |

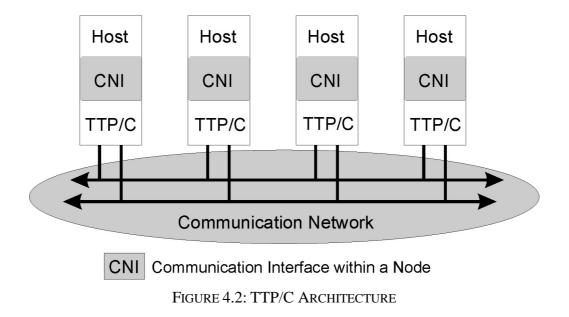

| 4.4 TIME-TRIGGED PROTOCOL TTP/C                           |          |

| 4.5 FlexRay Protocol                                      |          |

| 4.6 CONTROLLER AREA NETWORK PROTOCOL CAN                  |          |

| 4.7 TTCAN - TIME TRIGGERED COMMUNICATION ON CAN           |          |

| CHAPTER 5                                                 | 74       |

| THE THESIS GOALS AND APPROACHES                           | 74       |

| 5.1 Overview                                                                         |   |

|--------------------------------------------------------------------------------------|---|

| 5.2 SUMMARY OF GOALS                                                                 |   |

| 5.3 GOALS AND APPROACHES                                                             |   |

| 5.3.1 Enhance the fault tolerance capabilities of multiprocessor hard real-time      |   |

| systems                                                                              |   |

| 5.3.2 Guarantees required for fault-tolerant execution in real-time systems          |   |

| 5.3.3 Study the tradeoff between fault tolerance capability and resource utilization |   |

| of hard real-time systems77                                                          |   |

| 5.3.4 Use techniques to improve system utilization                                   |   |

| 5.3.5 Define resiliency of the systems                                               |   |

| 5.3.6 Estimate the overhead introduced by the real-time fault-tolerant               |   |

| communication protocol                                                               |   |

| 5.4 Summary                                                                          |   |

| CHAPTER 6                                                                            | 3 |

| IMPROVING FAULT TOLERANCE IN HRTSS                                                   | 3 |

| 6.1 OVERVIEW                                                                         |   |

| 6.2 System, Task and Fault Models                                                    |   |

| 6.3 FAULT TOLERANCE AND RATE MONOTONIC SCHEDULING IN MULTIPROCESSOR                  |   |

| SYSTEMS                                                                              |   |

| 6.4 RATE MONOTONIC SCHEDULING APPLIED TO THE CAN BUS                                 |   |

| 6.5 Improving Reliability in a CAN bus90                                             |   |

| 6.5.1 Applying Fault tolerance requisites to a CAN bus                               |   |

| 6.5.2 Limiting the maximum transfer rate of the CAN bus                              |   |

| 6.6 FORMAL VERIFICATION OF RMCAN                                                     |   |

| 6.6.1 Modeling Premises                                                              |   |

| 6.6.2 Formal verification of the capability to guarantee message delivery and of     |   |

| the recovery and fault tolerance capability of the protocol                          |   |

| 6.7 Comparison of Real-Time Fault-Tolerant Communication Protocols –                 |   |

| ADVANTAGES OF THE PROPOSED METHOD                                                    |   |

| 6.8 TARGET APPLICATION: DESIGN OF AN UNINTERRUPTIBLE POWER SUPPLY                    |   |

| 6.8.1 UPS Functionality                                                              |   |

| 6.8.2 UPS Architecture and Operating Modes                                           |   |

| 6.8.3 Fault tolerant support         |  |

|--------------------------------------|--|

| 6.8.3.1 Tests and Results            |  |

| 6.8.4 UPSs' parallelism              |  |

| 6.9 SUMMARY                          |  |

| CHAPTER 7                            |  |

| CONCLUSIONS                          |  |

| 7.1 SUMMARY                          |  |

| 7.2 Future Work                      |  |

| APPENDIX A                           |  |

| UPS ARCHITECTURE AND OPERATION MODES |  |

| REFERENCES                           |  |

# **List of Figures**

| FIGURA A. DEFINIÇÃO DO MODELO DE FALHAS                                  |           |

|--------------------------------------------------------------------------|-----------|

| FIGURA B. BARRAMENTO CAN EM UMA PLANTA DE CONTROLE                       |           |

| FIGURA C. VISÃO GERAL DA ARQUITETURA                                     |           |

| FIGURA D. OPERAÇÃO DE UM NO-BREAK UTILIZANDO RMCAN                       |           |

| FIGURE 1.1: CAN SALES EVOLUTION                                          |           |

| FIGURE 2.1: ATTRIBUTES OF FAULT CHARACTERISTICS                          |           |

| FIGURE 2.2: INFORMATION REDUNDANCY                                       |           |

| FIGURE 2.3: A TOP-LEVEL VIEW OF THE SYSTEM DESIGN PROCESS                |           |

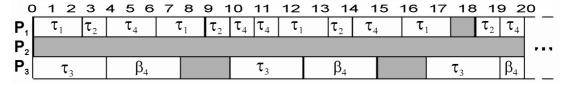

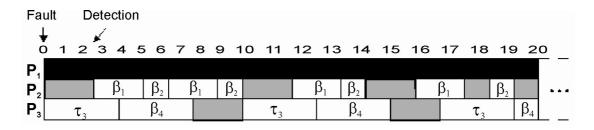

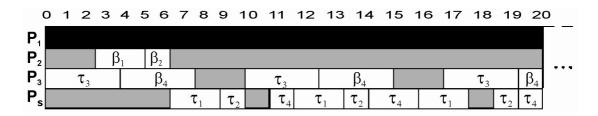

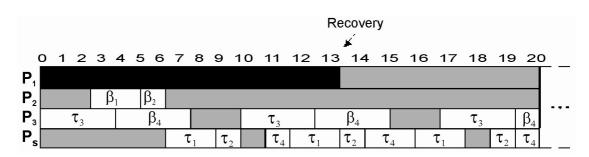

| FIGURE 3.1: PROCESSOR FAULT AND RECOVERY IN THE DEADLINE.                | 61        |

| FIGURE 3.2: FAULT-FREE SYSTEM STATUS                                     |           |

| FIGURE 3.3: FAULT RECOVERY FROM $P_1$ executed by $P_2$                  |           |

| FIGURE 3.4: PROCESSOR P <sub>1</sub> REPLACED BY P <sub>s</sub>          |           |

| FIGURE 3.5: DEADLINE RECOVERS P <sub>1</sub>                             |           |

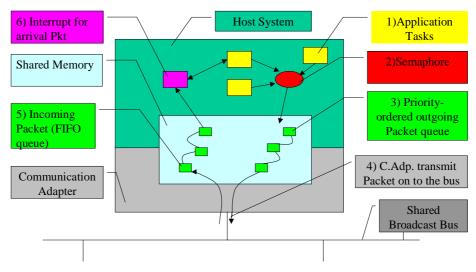

| FIGURE 4.1: SHARED BROADCAST BUS                                         |           |

| FIGURE 4.2: TTP/C ARCHITECTURE                                           |           |

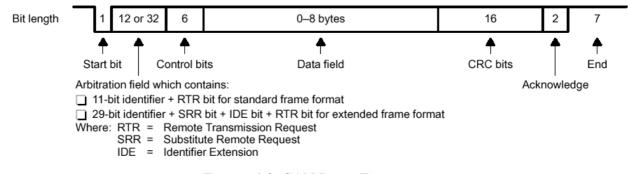

| FIGURE 4.3: CAN DATA FRAME                                               |           |

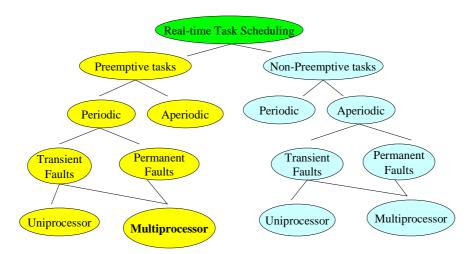

| FIGURE 5.1: SCHEDULING PROBLEMS                                          | 76        |

| FIGURE 5.2: FAULT CLASSIFICATION                                         | 77        |

| FIGURE 5.3 OVERLOADING TECHNIQUES                                        |           |

| FIGURE 5.4: HARDWARE IMPLEMENTATION                                      |           |

| FIGURE 5.5: TMS320LF2407 BLOCK DIAGRAM                                   |           |

| FIGURE 6.1: FAULT MODEL DEFINITION                                       |           |

| FIGURE 6.2: CAN BUS IN A CONTROL PLANT                                   |           |

| FIGURE 6.3: RMCAN REPRESENTATION                                         |           |

| FIGURE 6.4: PROPERTIES CHECKED FOR THE RECOVERY AND FAULT TOLERANCE CAPA | BILITY OF |

| THE PROTOCOL                                                             |           |

| FIGURE 6.5: UPS FUNCTIONALITY – INPUT AND OUTPUT VOLTAGES                |           |

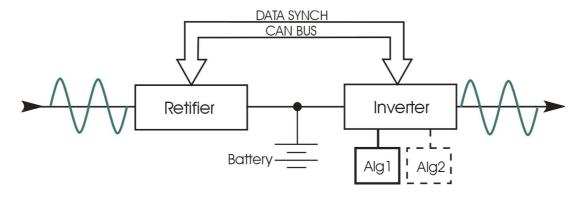

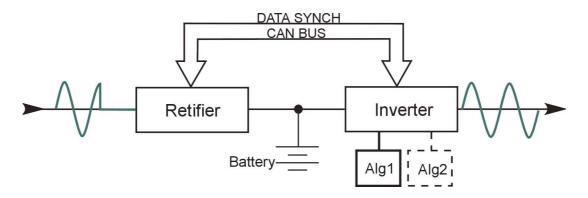

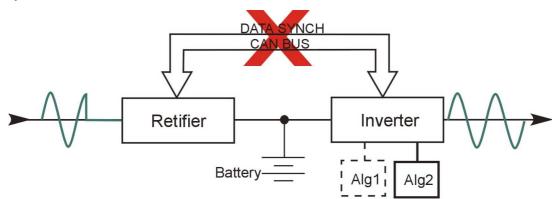

| FIGURE 6.6: UPS ARCHITECTURE - DATA SYNCH THROUG A CAN BUS               |           |

| FIGURE 6.7: UPS ARCHITECTURE – OPERATION IN A POWER FAULT SCENARIO       |           |

| FIGURE 6.8: UPS ARCHITECTURE - OCCURRENCE OF A CAN FAULT IN A POWER FAU   | JLT |

|---------------------------------------------------------------------------|-----|

| SCENARIO                                                                  | 102 |

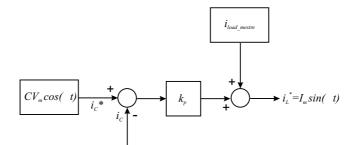

| FIGURE 6.9: DETERMINING THE REFERENCE CURRENT OF THE SLAVE UPSS           | 105 |

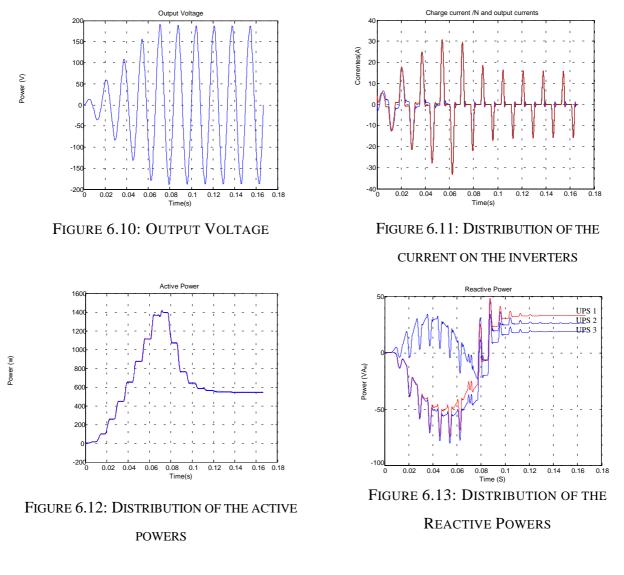

| FIGURE 6.10: OUTPUT VOLTAGE                                               | 106 |

| FIGURE 6.11: DISTRIBUTION OF THE CURRENT ON THE INVERTERS                 | 106 |

| FIGURE 6.12: DISTRIBUTION OF THE ACTIVE POWERS                            | 106 |

| FIGURE 6.13: DISTRIBUTION OF THE REACTIVE POWERS                          | 106 |

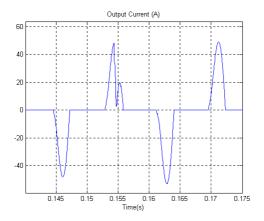

| FIGURE 6.14: TOTAL CURRENT IN THE LOAD DURING A FAILURE IN THE UPS MASTER | 107 |

| FIGURE 6.15: VOLTAGE IN THE LOAD DURING A FAILURE IN THE UPS MASTER       | 107 |

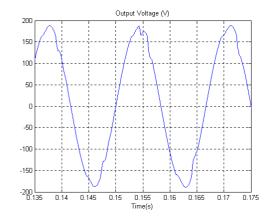

| FIGURE A1: UPS ARCHITECTURE CONTROL DETAILED VIEW                         | 113 |

# **List of Tables**

| TABLE | TABLE 1.1: 1999 WORLD MARKET FOR MICROPROCESSORS [16]    28 |               |           |         |       | 28     |       |     |         |    |

|-------|-------------------------------------------------------------|---------------|-----------|---------|-------|--------|-------|-----|---------|----|

| TABLE | 6.1:                                                        | COMPARISON    | BETWEEN   | TTP/C,  | CAN,  | TTCAN, | RMCAN | AND | FLEXRAY |    |

| PRO   | отосо                                                       | LS            |           | •••••   | ••••• |        |       |     |         | 99 |

| TABLE | 6.2: R                                                      | ESULTS OBTAIN | ED FROM A | N 80KVA | UPS   |        |       |     | 1       | 03 |

# Glossary

| Term                                  | First appears | Notes                                                     |  |

|---------------------------------------|---------------|-----------------------------------------------------------|--|

|                                       | on page       |                                                           |  |

| ALU                                   | 27            | Arithmetic Logical Unit                                   |  |

| В                                     | 72            | Blocking time                                             |  |

| Cj                                    | 72            | Worst-case time taken to physically transmit the message  |  |

| , , , , , , , , , , , , , , , , , , , |               | on the bus.                                               |  |

| C <sub>m</sub>                        | 72            | Transmission Delay                                        |  |

| CAN                                   | 14            | Controller Area Network                                   |  |

| CPU                                   | 12            | Central Processing Unit                                   |  |

| CRC                                   | 28            | Cyclic Redundancy Check                                   |  |

| CSMA/CA                               | 46            | Carrier Sense Multiple Access with Collision Avoidance    |  |

| CSMA/CD                               | 46            | Carrier Sense Multiple Access with Collision Detection    |  |

| CTT                                   | 17            | Completion Time Test                                      |  |

| D <sub>m</sub>                        | 72            | Deadline of message m.                                    |  |

| DMA                                   | 49            | Direct Memory Access                                      |  |

| DSP                                   | 12            | Digital Signal Processor                                  |  |

| E(R <sub>m</sub> )                    | 73            | Probable bound on the error recovery overheads before a   |  |

|                                       |               | message m arrives at its destination                      |  |

| FIFO queue                            | 49            | First In First Out queue                                  |  |

| FlexRay                               | 14            | FlexRay Protocol                                          |  |

| FTRMFF                                | 17            | Fault-Tolerant Rate-Monotonic First-Fit                   |  |

| $h_p(m)$                              | 72            | Set of all messages in the system of higher priority than |  |

| *                                     |               | message m.                                                |  |

| HRTSs                                 | 14            | Hard Real-Time Systems                                    |  |

| IMAGES                                | 16            | Integrated Modeling for Analysis and Generation of        |  |

|                                       |               | Embedded Software                                         |  |

| I/O                                   | 32            | Input/Output                                              |  |

| J <sub>j</sub>                        | 72            | Jitter on the queuing of message m                        |  |

| m                                     | 72            | A Message                                                 |  |

| MOBIES                                | 16            | Model-Based Integration of Embedded Systems               |  |

| NMI                                   | 26            | Non-Maskable Interrupt                                    |  |

| R <sub>m</sub>                        | 72            | Worst-case response time                                  |  |

| RAM                                   | 21            | Random Access Memory                                      |  |

| RM                                    | 34            | Rate-Monotonic                                            |  |

| RMA                                   | 17            | Rate-Monotonic Algorithm                                  |  |

| RMCAN                                 | 21            | Rate-Monotonic Controller Area Network                    |  |

| RMFF                                  | 17            | Rate-Monotonic First Fit heuristic                        |  |

| RMS                                   | 33            | Rate-Monotonic Scheduling                                 |  |

| ROM                                   | 27            | Read-Only Memory                                          |  |

| SRTSs                                 | 13            | Soft Real-Time Systems                                    |  |

| $	au_{\mathrm{bit}}$                  | 72            | Time taken to transmit a bit on CAN                       |  |

| Tj             | 72 | The period of message m                                  |  |

|----------------|----|----------------------------------------------------------|--|

| t <sub>m</sub> | 72 | Longest time a message can be queued in a station an be  |  |

|                |    | delayed because other messages are being sent on the bus |  |

| TDMA           | 18 | Time Division Multiple Access protocol                   |  |

| TTA            | 49 | Time-Triggered Architecture                              |  |

| TTCAN          | 14 | Time-Triggered Controller Area Network                   |  |

| TTP/A          | 14 | Time-Triggered Protocol for class A                      |  |

| TTP/C          | 14 | Time-Triggered Protocol for class C                      |  |

# **Resumo em Português**

## Introdução

Sistemas de tempo real são sistemas cuja correta execução depende não só do resultado correto da computação, mas também do instante de tempo em que este resultado é alcançado. Exemplos de sistemas de tempo real incluem os processadores de sinais, controladores de vôos e de processos, aplicações em telecomunicações, sistemas automotivos e sistemas médicos de suporte à vida. Sistemas de tempo real críticos (HRTSs), mais especificamente, possuem restrições de tempo rígidas, e o não cumprimento dos prazos das tarefas pode ser catastrófico. Estes sistemas têm como premissas a confiabilidade, disponibilidade, segurança, desempenho, entre outas características. Falhas em tais sistemas podem ocasionar perdas humanas, ecológicas e econômicas.

Escalonamento e alocação de recursos em sistemas de tempo real são problemas difíceis em função das restrições de tempo das tarefas envolvidas. Tolerância a falhas é um requisito vital no desenvolvimento de sistemas de tempo real críticos. Políticas de escalonamento nestes sistemas devem garantir que as tarefas cumprirão seus prazos finais sob quaisquer circunstâncias, mesmo na presença de falhas transientes e permanentes. Uma característica de sistemas de tempo real está no fato de que estes sistemas devem ser capazes de prever que um prazo não será atendido e tomar as ações necessárias antes que uma pane ocorra. Os requisitos de tempo e o modelo de falhas dependem do conhecimento preciso da aplicações e do ambiente na qual esta está inserida.

A base de todas as técnicas de tolerância a falhas está relacionada ao conceito de redundância. Este conceito era implementado, inicialmente, através da simples replicação de componentes. Ao longo do tempo notou-se que outros tipos de redundância levam ao mesmo resultado e, muitas vezes, de forma mais eficiente.

Neste trabalho, uma análise de técnicas de tolerância a falhas no contexto de sistemas de tempo real multiprocessados é apresentada, incluindo escalonamento e protocolos de comunicação. Uma nova técnica baseada em escalonabilidade de tarefas e incorporando redundância de tempo foi proposta, podendo esta ser utilizada em conjunto com redundâncias de hardware e software. O trabalho foi desenvolvido sobre o protocolo CAN (Controller Area

Network) por se tratar de um protocolo que está presente em mais de 90% das aplicações envolvendo microcontroladores e DSPs que incorporam protocolos de tempo real. Um problema conhecido do barramento CAN está na entrega de mensagens de baixa prioridade, a qual pode ser comprometida caso mensagens de mais alta prioridade ocupem todo o *bandwidth*. Foi proposta assim uma extensão ao protocolo CAN através da aplicação de técnicas que buscam melhorar a confiabilidade do protocolo.

A extensão proposta, denominada RMCAN, provê garantias de falhas no barramento CAN serão toleradas. Para tanto, é definida uma taxa máxima de transmissão para cada nó, ao invés de utilizarmos *slots* de tempo pré-definidos (como é feito no TTP/C). Com esta condição de contorno, as transmissões de um nó não ficam restritas a um *slot* de tempo, mas podem ocorrer até que a taxa máxima de transmissão seja atingida.

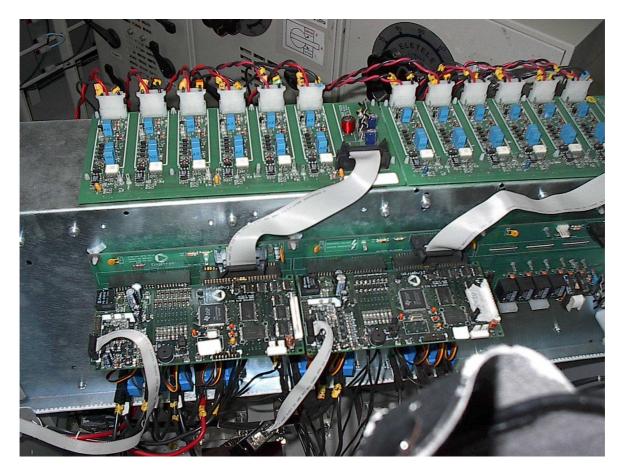

Outra importante contribuição deste trabalho está na definição de uma arquitetura tolerante à falhas de tempo real baseada em DSPs, onde um conjunto de processadores executando em paralelo troca informações através de um barramento CAN.

### **Trabalhos relacionados**

Um algoritmo de escalonamento consiste em um conjunto de regras que determinam a tarefa a ser executada em um momento em particular. A abordagem tradicionalmente adotada é aquela onde o escalonamento é preemptivo e baseado em prioridades. Nesta abordagem, as tarefas possuem prioridades que lhes são atribuídas dinâmica ou estaticamente. Em um determinado momento, se uma tarefa de mais baixa prioridade está sendo executada e uma tarefa de maior prioridade entra na fila, a tarefa de menor prioridade é colocada em espera enquanto o processador é liberado para a execução da tarefa de maior prioridade. Desta forma, a especificação de algoritmos de escalonamento preemptivos baseados em prioridades. Um algoritmo é dito estático se as prioridades são atribuídas uma única vez; da mesma forma, um algoritmo é dito dinâmico se as prioridades são alteradas entre uma requisição e outra. Existem ainda algoritmos mixtos onde algumas tarefas têm suas prioridades definidas estaticamente enquanto outras têm suas prioridades definidas dinamicamente. Caso tenhamos as prioridades definidas sistematicamente, utilizando a abordagem *rate-monotonic*, por exemplo, limites de utilização podem ser determinados. Nesta situação, se um conjunto de

tarefas não exceder os limites, podemos dizer que as tarefas poderão ser executadas sem que os prazos finais sejam perdidos.

#### Teoria Rate-monotonic

O termo "análise *rate-monotonic*" surgiu em 1973 através da publicação de um artigo denominado "Scheduling Algorithms for Multiprogramming in a Hard Real Time Environment" por Liu e Layland [5]. Este artigo propôs o que seria a base para um teste simples a ser aplicado em sistemas de tempo real para se determinar se um conjunto de tarefas seria executado antes de seus prazos finais. Foram considerados prazos finais das tarefas o final de seus períodos, e nenhuma tarefa poderia bloquear o sistema enquanto tivesse sendo executada. Além disto, foram atribuídas única e monotonicamente prioridades a cada tarefa do conjunto.

O algoritmo *rate-monotonic* (RMA) consiste em um algoritmo de escalonamento de tarefas que atribui mais altas prioridades a tarefas com menor período; é ótimo se o conjunto de tarefas for independente [5]. Assume-se que todas as tarefas no sistema são periódicas, têm seus prazos finais no final de seus períodos e são totalmente independentes umas das outras[51].

Vários trabalhos foram desenvolvidos baseados na teoria RMA: Joseph and Pandya[10] demonstraram o Completion Time Test (**CTT**) para verificar a escalonabilidade de um conjunto fixo de tarefas periódicas em um processador. Bertossi e Mancine [15] propuseram o Faut-Tolerant Rate-Monotonic First-Fit (**FTRMFF**) para prover tolerância a falhas a um HRTS utilizando um sistema multiprocessado onde cada tarefa tem uma cópia ativa ou passiva em outro processador e todo o conjunto de tarefas é escalonado pelo RMFF, suportando falhas *fail-stop* de um ou mais processadores.

#### Rate-monotonic e tolerância a falhas

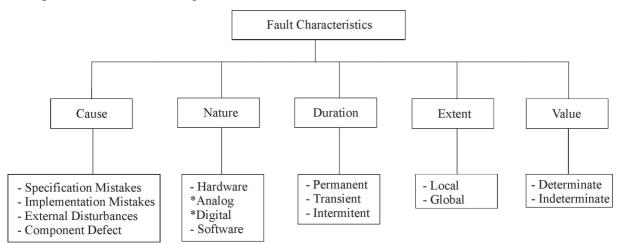

Em função da natureza crítica das tarefas em sistemas de tempo real, é essencial que falhas sejam toleradas. Uma falha em um sistema pode se manifestar de várias formas, tornando seu diagnóstico muitas vezes complicado. Buscando reduzir este problema, um sistema pode ser projetado de forma a seguir um modelo de falhas, tornando o problema de diagnosticá-las simplificado. Nem todas as falhas que ocorrem em um sistema são tratadas

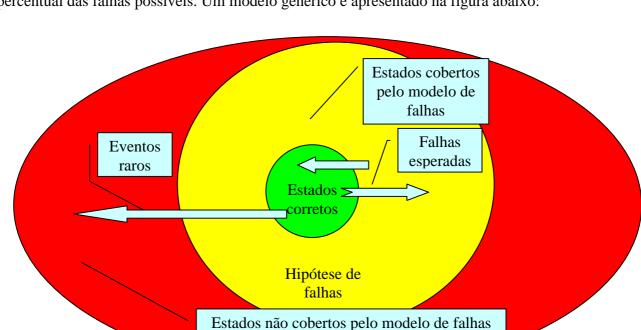

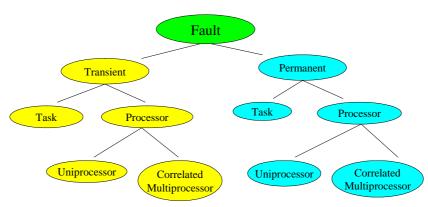

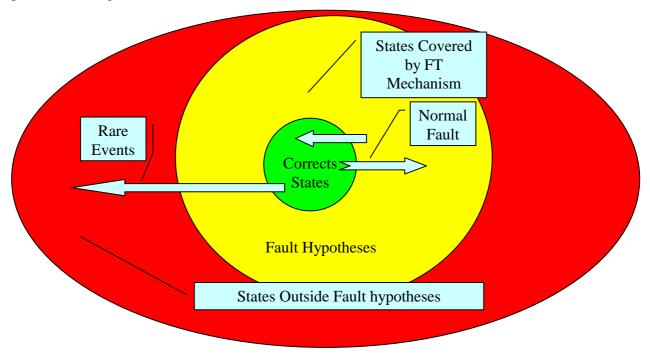

pelo modelo de falhas, sendo que existem modelos de falhas que cobrem um grande percentual das falhas possíveis. Um modelo genérico é apresentado na figura abaixo:

FIGURA A. DEFINIÇÃO DO MODELO DE FALHAS

Falhas transientes são toleradas, geralmente, utilizando-se redundância de tempo, a qual involve a re-execução das tarefas que estavam executando durante a falha transiente.

Ghosh propôs em [48] um algoritmo onde a execução de tarefas de tempo real é garantida mesmo na ocorrência de falhas transientes e intermitentes. A abordagem geral para se tolerar falhas consiste em reservar tempo suficiente no escalonamento de forma que qualquer instância de uma tarefa possa ser re-executada caso uma falha ocorra durante sua execução. Se nenhuma falha ocorrer, as tarefas serão executadas seguindo o esquema usual do *rate-monotonic*.

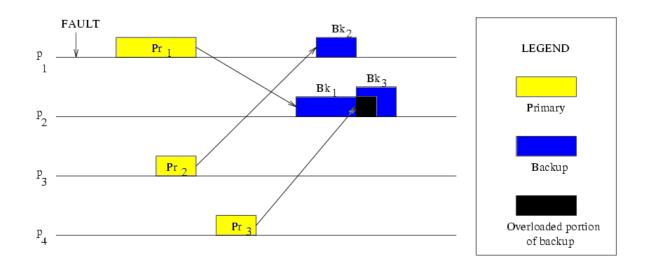

Ghosh propôs ainda um algoritmo para escalonamento de tarefas tolerante a falhas em sistemas multiprocessados. O algoritmo garante a execução de uma tarefa antes do prazo final mesmo na presença de falhas no processador.

#### Protocolos de comunicação de tempo real tolerantes à falhas

Um serviço essencial provido por arquiteturas distribuídas de tempo real tolerantes à falhas é a troca de informação entre os componentes distribuídos. Estas arquiteturas têm como importante componente o barramento de comunicação e protocolos utilizados no

controle e comunicação estão entre seus principais mecanismos. Em sistemas distribuídos de tempo real, a comunicação entre diferentes processadores deve ocorrer em um tempo prédeterminado.

Barramentos redundantes são utilizados com frequência em ambientes críticos para lidar com as falhas nos dispositivos. Existem vários protocolos de comunicação utilizados em sistemas de tempo real, cada qual apresentando uma complexidade. Exemplos mais representativos são o protocolo TTP/C (Time-Triggered Protocol) [20] FlexRay [10], CAN (Controller Area Network) [8] and TTCAN (Time-Triggered CAN) [5][7][15]. Estes protocolos têm sido utilizados na indústria da aviação (Airbus e Boeing), na indústria automotiva (BMW e a Audi), entre outras.

Alguns protocolos citados acima são basicamente "time-triggered", como por exemplo o TTP/C. Isto significa que todas as atividades envolvendo o barramento e os componentes anexados a ele são baseadas na passagem do tempo. Outros protocolos são basicamente "event-triggered", como por exemplo o CAN; nestes protocolos as atividades envolvendo o barramento são baseadas na ocorrência de eventos, respondendo a estímulos externos e interagindo com o ambiente. Existem ainda protocolos mistos, como o TTCAN e o FlexRay, onde os dois conceitos se misturam.

## Abordagem proposta e desenvolvimento do trabalho

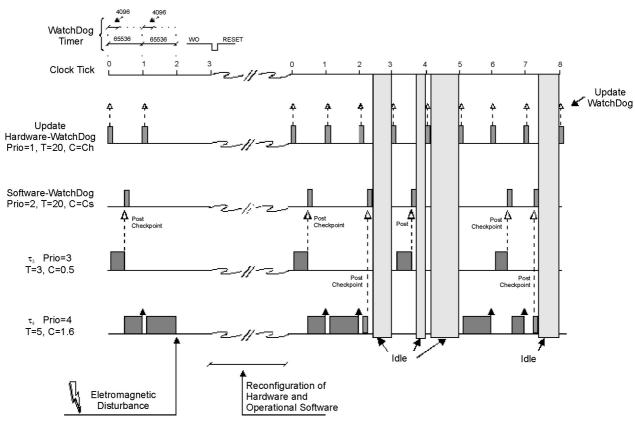

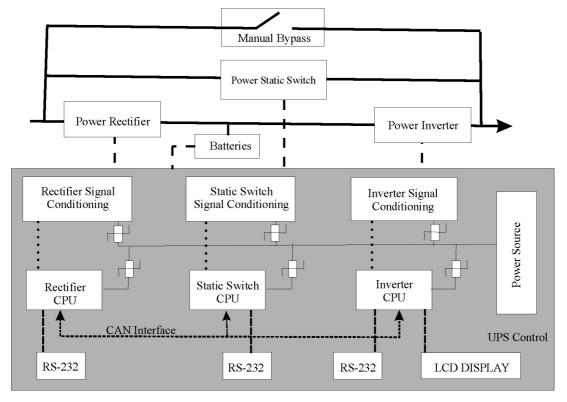

Sempre que um sistema tolerante à falhas é projetado, uma forma de redundância deve ser incorporada. Escalonabilidade de tarefas e redundância de tempo são ferramentas importantes para se garantir que os requisitos de tolerãncia a falhas sejam atendidos para um determinado sistema. Com o custo de processadores reduzindo gradativamente e o desenvolvimento de inúmeros protocolos de comunicação de tempo real, tais como CAN [29], TTP/C [26], TTP/A [25] e FlexRay [27], tornou-se importante pesquisar aspectos relacionados a sistemas de tempo real multiprocessados, onde testes de escalonabilidade devem garantir a execução de todas as tarefas do conjunto antes de seus prazos finais e considerando um modelo de falhas.

O principal objetivo deste trabalho é garantir requisitos de tolerância a falhas em sistemas multiprocessados de tempo real crítico. Os recursos utilizados para otimizar estes requisitos são a escalonabilidade de tarefas e redundância de tempo. Este trabalho apresenta

técnicas para se melhorar a capacidade de tolerar falhas de tais sistemas incorporando ainda redundância de processadores e protocolos de comunicação de tempo real.

A abordagem utilizada consiste em prover tolerância à falhas através do escalonamento de tarefas e da adição de *slacks* de tempo no processamento. Se uma falha for detectada pelo sistema operacional durante a execução de uma tarefa, esta tarefa deverá ser reexecutada dentro deste *slack* de tempo ou uma tarefa backup deve ser ativada para recuperação da falha.

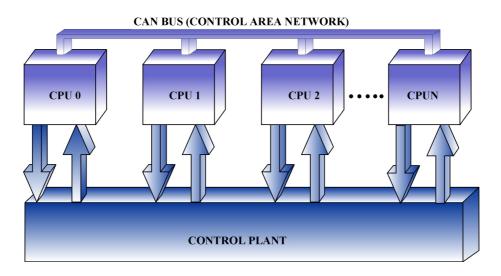

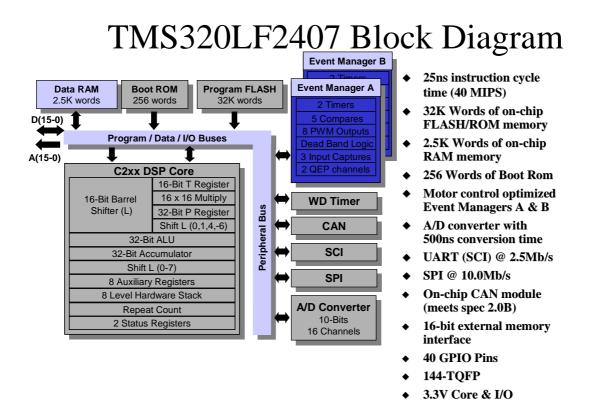

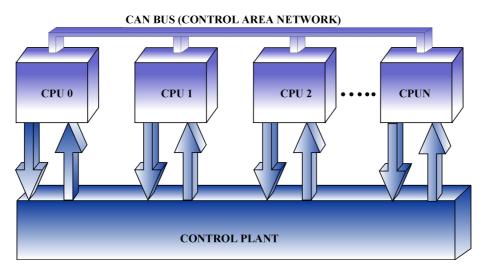

A implementação de um sistema multiprocessado baseado em DSPs interconectado por um barramento CAN é apresentada.

FIGURA B. BARRAMENTO CAN EM UMA PLANTA DE CONTROLE

Na figura acima, cada processador executa aplicações de tempo real periódicas escalonadas através do RMA com tempo máximo de execução e período de execução prédefinidos. Por se tratarem de tarefas de controle, consistem em um conjunto de tarefas independentes, onde o início de uma tarefa não depende da execução de nenhuma outra tarefa.

O modelo de falhas foi definido considerando as seguintes características do sistema:

(F1) Falhas transientes e permanentes podem ocorrer na execução de uma tarefa ou até mesmo em um processador;

(F2) Apenas falhas transientes do barramento de comunicação são toleradas;

(F3) Processadores livre de falhas podem comunicar entre si;

(F4) O hardware provê isolamento das falhas no sentido de que uma falha em um processador não provocará falhas em outros processadores;

(F5) A falha de um processador é detectada pelos demais através da não execução de alguma tarefa alocada para o processador que falhou, e é sinalizada pela ausência de mensagem no barramento CAN.

O modelo inclui falhas que podem ocorrer no barramento ou no protocolo de comunicação, uma vez que estes influenciam o funcionamento do sistema como um todo. Considerando o barramento CAN, é necessário garantirmos que um pacote será entregue dentro do seu prazo final ou, no pior caso, que o remetente saberá que o envio foi sem sucesso e que nova transmissão deverá ser feita. Uma mensagem deve ser retransmitida um número de vezes no caso de falha na transmissão e ainda assim cumprir seu prazo final. No barramento CAN, uma falha é sinalizada através da ausência de mensagens, isto é, se uma mensagem não for recebida pelos processadores dentro de um intervalo de tempo, uma falha no processador primário é assumida e a recuperação desta falha é feita através de uma tarefa backup. Quaisquer erros nas mensagens podem indicar que uma falha ocorreu, e uma tarefa alternativa será executada consequentemente, evitando assim uma pane no sistema. Falhas permanentes no barramento CAN não são toleradas, causando uma interrupção no processo de comunicação.

## Análise do tempo de transmissão de mensagens no barramento CAN

O algoritmo de escalonamento dinâmico utilizado pelo protocolo CAN é praticamente idêntico aos algoritmos de escalonamento comumente utilizados em sistemas de tempo real para escalonar tarefas em processadores [18]. A análise do comportamento destes sistemas pode ser aplicada quase que sem modificações na solução do problema de se determinar o pior caso do tempo de transmissão de uma dada mensagem no barramento CAN.

Tindell *et. al.* [19] desenvolveu uma análise sobre o barramento CAN baseada na análise *rate-monotonic*, mostrando como calcular o pior tempo de resposta para mensagens transmitidas pelo barramento.

A ocorrência de erros de transmissão também deve ser considerada. Em um barramento CAN, um erro detectado tanto pelo emissor quanto pelo receptor da mensagem é sinalizado ao emissor, o qual deve retransmitir a mensagem.

Um problema conhecido do protocolo CAN é o fato de não se poder garantir que mensagens de mais baixa prioridades serão entregues antes do seu prazo final em caso de sobrecarga. Enquanto o protocolo CAN é muito eficiente na transmissão de dados mais urgentes, estas mensagens podem sobrecarregar o barramento de tal forma que as mensagens de mais baixa prioridade não conseguirão cumprir seus prazos de transmissão [11][12][13].

Neste sentido, é necessário garantirmos que a sobrecarga não ocorrerá, para que todos os prazos finais sejam cumpridos.

#### Aplicando conceitos de tolerância à falhas ao protocolo CAN

Falhas no barramento CAN implicam na re-transmissão de mensagens ou até mesmo na execução de ações alternativas para a reconfiguração do barramento.

Ghosh [6] desenvolveu um esquema para recuperação de uma ou mais falhas que garante a re-execução de qualquer tarefa assim que uma falha for detectada. Os mesmos conceitos apresentados por Ghosh foram aplicados ao protocolo CAN, buscando garantir que uma mensagem seja re-transmitida quando uma falha na transmissão for detectada. Estes conceitos, utilizados em escalonamento *rate-monotonic*, foram aplicados ao barramento CAN uma vez que:

[S1] As mensagens são independentes ou assíncronas.

[S2] As mensagens têm suas prioridades definidas pelo RMA.

[S3] Uma mensagem de mais alta prioridade não deve ocupar todo o *bandwidth* do barramento impedindo que mensagens de mais baixa prioridade executem

Segundo a abordagem apresentada por Ghosh, deve ser mantido um intervalo de tempo suficiente para que uma mensagem seja re-transmitida. Caso nenhuma falha ocorra, as mensagens são transmitidas normalmente, seguindo o escalonamento *rate-monotonic* e este *slack* não é utilizado. Caso ocorra algum erro no processo de transmissão da mensagem, esta deve ser re-transmitida antes do fim do seu período de transmissão. Para que os conceitos apresentados por Ghosh pudessem ser aplicados ao protocolo CAN, as seguintes condições devem ser satisfeitas:

[S1] Deve ser reservado um intervalo de tempo suficiente para que cada instância de cada mensagem possa ser re-transmitida.

[S2] Quando uma instância de uma mensagem é transmitida, uma quantidade suficiente do *slack* disponível dentro do seu período deve estar disponível para que esta mensagem possa ser re-transmitida antes do prazo final, caso uma falha seja detectada.

[S3] Quando uma mensagem é re-transmitida, esta não deve interferir na transmissão de nenhuma outra mensagem, ou seja, a re-transmissão de uma mensagem de mais alta prioridade não interferirá no cumprimento dos prazos finais de outras mensagens.

## Limitação da taxa máxima de transferência por nó no barramento CAN

Considerando os resultados obtidos por Tindell em [69], onde mostrou-se ser possível determinar o tempo máximo de transmissão para o barramento CAN no pior caso, foi demonstrado no Capítulo 6 que as três premissas podem ser atendidas.

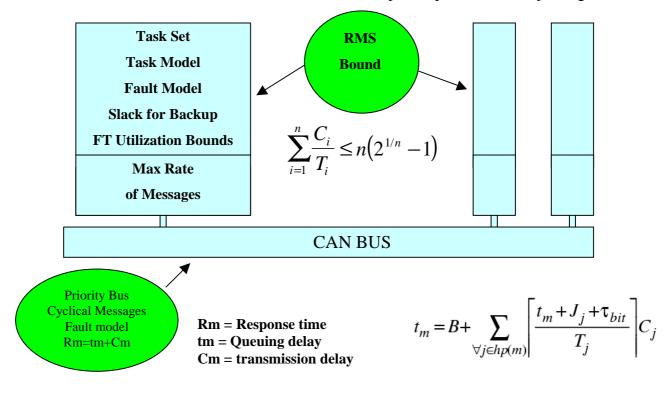

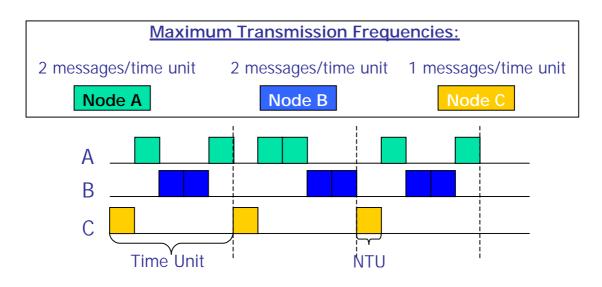

Foi proposta assim uma extensão ao protocolo CAN, denominada **Rate Monotonic CAN (RMCAN)**, onde foram definidos slacks de tempo de tamanho suficiente para que, mesmo no pior caso, todas as mensagens possam ser transmitidas ou até mesmo retransmitidas se necessário. Cada mensagem tem sua transmissão limitada a um tempo máximo e um período pré-definido, sendo definido um limite para a taxa máxima de transmissão para um nó do barramento CAN. Podemos assim garantir que é possível re-transmitir uma mensagem que apresentou falha e ainda cumprir o prazo final. Desta forma, ao invés de limitar a transmissão a um período pré-definido, como é feito pelo TTP/C, um nó pode distribuir sua transmissão durante vários intervalos de tempo até que seu limite seja atingido.

#### FIGURA C. VISÃO GERAL DA ARQUITETURA

A independência das mensagens é garantida pelo fato de se tratarem de mensagens geradas por tarefas de controle que são independentes. Uma visão geral da arquitetura, considerando todos os conceitos apresentados, é mostrada na figura abaixo.

# Comparação de protocolos de tempo real tolerantes à falhas

Podemos dizer que o protocolo TTP/C provê o projeto estático assegurando um tempo máximo de transmissão para todas as mensagens, mas ao mesmo tempo ele apresenta baixa flexibilidade uma vez que a largura de banda é distribuída em tempo de projeto através da atribuição de frames de tamanho específico a cada nó. Em um barramento CAN, por outro lado, as prioridades podem ser determinadas em tempo de execução através da atribuição de identificadores únicos e um controle completo da aplicação sobre a distribuição da largura de banda disponível. O protocolo CAN é um protocolo altamente flexível e largamente disponível, apesar de que algumas extensões devem ser feitas para se garantir um mecanismo confiável para se construir sistemas tolerante à falhas confiáveis. TTCAN é um compromisso e representa a necessidade de evolução do CAN, para que sobrecargas no barramento possam ser tratadas corretamente sem prejudicar a transmissão de mensagens. Por outro lado, a sincronização de nós exigida pelo TTCAN não é uma tarefa simples, exigindo hardware adicional. RMCAN foi desenvolvido com o objetivo de se obter a eficiência do TTCAN, mas sem incorporar nenhum hardware adicional ou outras restrições. Tanto o TTCAN quanto o RMCAN podem ser implementados utilizando controladores CAN. No caso do RMCAN, o controle da taxa de transmissão é feito por software, simplificando a implementação do protocolo. O protocolo FlexRay pode ser considerado o estado da arte em se tratando de protocolos de tempo real tolerantes a falhas, apesar de ainda não ter sido lançado no mercado. É um protocolo que promete uma taxa de transmissão maior do que o TTCAN e maior flexibilidade se comparado ao TTP/C.

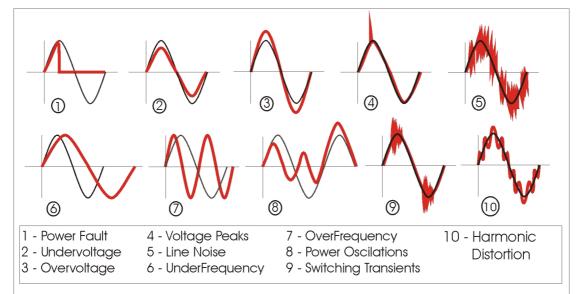

# Estudo de caso – Utilização do RMCAN em um sistema de alimentação de energia sem interrupções

Um no-break é um exemplo de sistema de tempo real crítico onde mecanismos de tolerância à falhas são essenciais. A função primária de um no-break é garantir continuidade de operação especialmente durante falhas de energia ou perturbações no fornecimento de energia elétrica.

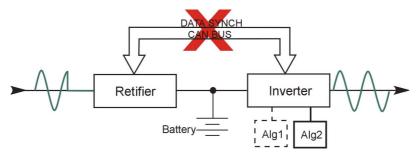

Uma aplicação onde o protocolo RMCAN foi utilizado consiste em um no-break trifásico de 80kVA, o qual deve fornecer energia sem interrupções às suas cargas mesmo quando uma falha no fornecimento de energia pela companhia de energia elétrica ocorrer.

A operação do no-break é controlada por lógica microprocessada: todas as tarefas são executadas por três CPUs independentes (retificador, inversor e chave estática), cada qual consistindo de um DSP. A escolha de DSPs para esta aplicação foi feita em função de características da própria aplicação. Um número maior de CPUs poderia ser utilizado considerando, por exemplo, redundância de hardware.

Apesar das CPUs operarem de forma autônoma, estas trocam informações entre si através de uma interface CAN, permitindo assim a monitoração e controle das informações. O protocolo RMCAN foi utilizado internamente para comunicação entre os processadores. Falhas de leitura de parâmetros em um dos processadores são repassadas aos outros, que tomam as ações devidas.

FIGURA D. OPERAÇÃO DE UM NO-BREAK UTILIZANDO RMCAN

A figura acima representa o processo de tratamento de uma falha no barramento CAN. Como as CPUs do retificador e inversor trocam informações periodicamente, o não recebimento de uma mensagem indica uma falha no barramento. Caso a re-execução indique que a falha permanece, é executado um algoritmo alternativo de forma que seja possível tolerar determinada falha. Falhas permanentes no barramento não são toleradas. A colocação de duas ou mais unidades de fontes de alimentação em paralelo fornece ao sistema uma maior tolerância a falhas aumentando substancialmente a confiabilidade. Entretanto, como os módulos de potência não são idênticos, as correntes fornecidas por cada módulo são diferentes. Alguns dos fatores que contribuem para este desequilíbrio são a tolerância dos componentes e a impedância dos circuitos de distribuição da corrente de saída de cada módulo. O circuito de controle das fontes de alimentação deve ser capaz de regular a tensão de saída das fontes de alimentação e simultaneamente distribuir uniformemente a corrente de carga entre os diversos módulo de potência.

Uma aplicação do método de paralelismo de conversores utilizando a técnica de controle do tipo mescre-escravo com comunicação através de interface CAN foi simulada, mostrando que é possível utilizarmos o RMCAN como protocolo de comunicação entre dois no-breaks em paralelo que utilizam o barramento CAN para sincronização. Foram simuladas situações onde ocorriam falhas no no-break mestre e no escravo, bem com falhas no barramento CAN.

## Conclusões

Tarefas em sistemas de tempo real devem cumprir seus prazos sob quaisquer circunstâncias, mesmo na presença de falhas transientes e permanentes. Neste trabalho utilizou-se conceitos como redundância de tempo e escalonamento de tarefas ao lidarmos com falhas em sistemas de tempo real.

Foram analisados ainda protocolos de comunicação de tempo real, sendo considerado o protocolo CAN por estar disponível em mais de 90% das aplicações envolvendo protocolos de tempo real. O protocolo CAN possui, muitas vezes, tempo de resposta não-determinístico para mensagens de baixa prioridade. O protocolo RMCAN foi proposto neste trabalho como uma extensão ao protocolo CAN, buscando assim resolver os problemas de não determinismo do protocolo bem com garantir que todas as mensagens serão entregues dentro de seus prazos finais ou até mesmo que não serão entregues, caso alguma falha ocorra. Limitou-se a taxa de transmissão de cada nó no barramento CAN tornando assim determinístico o tempo de transmissão de uma mensagem, mesmo para mensagens de baixa prioridade. Vale ressaltar que a transmissão de mensagens por um nó não ficou restrita a um intervalo de tempo, e sim a uma taxa máxima de transmissão. É possível assim garantir que haverá tempo suficiente para que uma mensagem seja transmitida, ou até mesmo re-transmitida, se necessário. Caso uma

mensagem não chegue ao seu destino, o destinatário saberá que uma falha ocorreu e que uma ação será executada de acordo com o modelo de falhas definido para a aplicação, como por exemplo, reconfiguração do barramento CAN.

As extensões ao protocolo CAN propostas aumentam a confiabilidade do protocolo bem como permitem que seja explorada sua grande presença no mercado. Foi feita ainda a verificação formal do RMCAN, garantindo assim que a transmissão das mensagens ocorrerá dentro do seu período, mesmo considerando que falhas ocorrerão no sistema.

# Chapter 1

# Introduction

## **1.1 Overview and Motivation**

Real-time systems are different from general purpose computing systems in several aspects. The processes in a real-time system have time related attributes such as ready times, deadlines, computation times and periods. A real-time system must provide predictable response times. Therefore, the worst case behavior of real-time systems is more important than the average response time. Real-time systems are systems that depend on the result of computation as well on the deadline by which this result is reached.

Architectures that support real-time applications tend to be specialized. However, the current trend is to develop more generic real-time architectures. The market trend itself, which demands an ever-increasing participation of microcontrollers and DSPs (digital signal processors), attests to the need for more generic real-time architectures. In 1992, the world market for conventional CPUs (Central Processing Units) was estimated at US\$ 4.9 billion while the market for of micro controllers and DSPs was US\$ 5.4 billion [20].

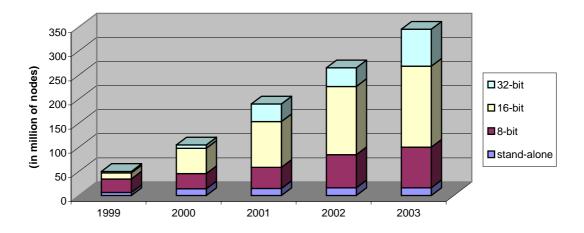

Table 1.1 shows the results of microcontrollers sales in 1999, when the number of microcontrollers completely outnumbered the desktop chips in terms of units shipped.

| Chip Category      | Number Sold  |

|--------------------|--------------|

| Embedded 4-bit     | 2000 million |

| Embedded 8-bit     | 4700 million |

| Embedded 16-bit    | 700 million  |

| Embedded 32-bit    | 400 million  |

| DSP                | 600 million  |

| Desktop 32/64 bits | 150 million  |

TABLE 1.1: 1999 WORLD MARKET FOR MICROPROCESSORS [16]

Only about 2% of the total number of chips used were in desktop and server systems, although they represent a much larger share of the revenues, since the processors per-chip costs is around two orders of magnitude of microcontrollers cost.

Most real-time systems are developed to attend a specific and complex need, requiring a high degree of fault tolerance, and they are typically embedded in a large system. Real-time systems typically include a high knowledge of the application and its environment [19], which is included statically in the project phase. The new generation of real-time systems must be designed to be dynamic and flexible regarding knowledge of the application and of the environment. They also need to guarantee the safety of the components and critical characteristics of the system [18].

Real-time systems can fail due to hardware and/or software faults, as well as by not answering within the required time constraints, which are usually imposed by the environment [13]. When the specification of a system demands that a certain task is executed by a certain deadline, the inability of the system to meet this specified constraint might be seen as a system fault, which can cause catastrophic consequences [30]. However, the simple approach of assuming the design method of a fault-tolerant system will treat missing a deadline as a system time fault; it will not attend to the needs of fault tolerance in real-time systems. The fundamental difference is that real-time systems have to be able to predict that the deadline will be missed, enabling thus the possibility of taking a certain action before such a fault occurs [13][18].

Fault tolerance is the attribute that systems must have to be able to accomplish tasks correctly in the presence of faults. Fault tolerance must be included in real-time system specifications, considering the software and hardware integration, and it must be integrated with timing constraints. Systems that demand high safety require formal proving techniques that will guarantee the characteristics of fault tolerance [19].

In this sense, fault tolerance and real-time specifications should be considered concomitantly in all phases of these types of projects. It is essential to adopt a project methodology that considers prediction in all phases, including time for fault detection, isolation, reconfiguration of the system, and recovery. Furthermore, requisites of fault tolerance can add even greater constraints to the system. For example, frequent tests and recovery routines increase the characteristic of fault tolerance; at the same time, however, they may increase the possibility of the system missing the specified deadline.

Due to the flexibility of the deadlines involved, soft real-time systems (SRTSs) rarely require proof that the system meets its real-time performance objective. Their timing requirements are often specified in probabilistic terms. Examples of such systems include electronic games, multimedia systems and telephone switches.

Hard real-time systems (HRTSs) have stringent timing constraints, and the consequence of missing task deadlines may be catastrophic. Fault tolerance is an especially vital requirement for HRTS development. Many embedded systems are hard real-time systems, and task deadlines in an embedded system are typically derived from the required responsiveness of the sensors and actuators, which are monitored and controlled by the embedded system. Examples of such systems are process controls, flight control, automotive systems, and life support systems. In this work, only HRTSs are considered.

Several methods of priority have already been proposed for providing fault-tolerance to HRTSs on a uniprocessor or multiprocessor platforms. Problems with task priority in HRTSs have already been shown as being NP-hard class problems [1], [2], and [3].

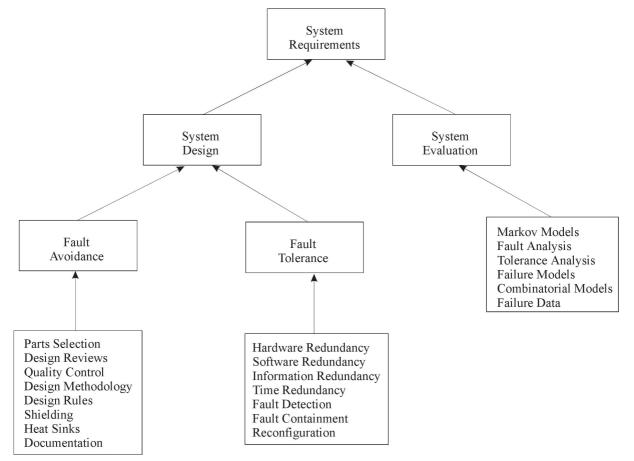

The base of all fault tolerance techniques is contained in the redundancy concept. Initially, in the early projects with fault tolerance requisites, it was thought that redundancy was obtained through a simple replication of components. In the course of time, it was noticed that, although redundancy was fundamental to acquire this capacity, there were other redundancy types which lead to the same result, in a perhaps more efficient way.

Whenever a fault-tolerant system is designed, a redundancy type must be incorporated into the equivalent system, which does not incorporate fault tolerance requisites. Since time is the central resource of any fault-tolerant hard real-time system, task schedulability and time redundancy become the basic tools to guarantee fault tolerance requisites for a given hard realtime system.

With processor costs dropping off and the emergent development of real-time communication protocols, such as CAN (Controller Area Network)[29], TTCAN (Time-Triggered Controller Area Network)[55], TTP/C (Time-Triggered Protocol for Class C)[26], TTP/A (Time-Triggered Protocol for Class A)[25] and FlexRay [27], a great need has consequently arisen to research multiprocessor hard real-time systems and fault tolerance, where the task schedulability needs to be guaranteed for a certain fault model specified.

Single processor schedulability analysis for fixed priority tasks has received considerable attention, and it has been considerably extended by relaxing many of the assumptions of the original computation model. Schedulability analysis for communications is much less complete.

Schedulability analysis of a distributed hard real-time system, where tasks with arbitrary deadlines communicate by message passing through a real-time bus, must consider not only the processing delays, but also the communications delays and the complications introduced by communications costs. The delays for messages being sent between processors must be accurately bounded, and the overheads due to communications must be strictly bounded.

Considering the communication issues, the spread adoption of the CAN protocol stimulated the development of this work, once it is present in most microcontrollers and DSPs incorporating real-time protocols. The sales of CAN nodes increased to a total of 200 million nodes (sold in 2001) and the conservative estimate for upcoming years is a continuous growth rate of at least 30% (Figure 1.1) [82].

FIGURE 1.1: CAN SALES EVOLUTION

However, a well-known problem of the CAN protocol is that the delivery of low priority messages may be compromised if the bus is flooded with higher priority messages, reason why its use is avoided in hard real-time applications. The use of the CAN protocol in hard real-time applications would bring an enormous benefit to developers, enlarging the possibilities for a hardware choice and simplifying the implementation process as a whole.

## **1.2 Thesis Goals**

This work presents an overview, extension and application of techniques to enhance the fault tolerance capability of multiprocessor hard real-time systems. An analysis of techniques for fault tolerance in the context of multiprocessor real-time systems is presented, including scheduling and communication protocols.

The main goal of this work is to guarantee fault-tolerance requisites for multiprocessor hard real-time systems. Since time is the central resource of any fault-tolerant hard real-time system, task schedulability and time redundancy become the basic tools to guarantee fault tolerance requisites for a given hard real-time system.

We explore how time redundancy can be used in conjunction with hardware and software redundancy to tolerate faults in hard real-time systems. The integration of these diverse techniques into a fault-tolerant multiprocessor real-time system is shown.

An holistic analysis on distributed embedded hard real-time systems must consider the worst-case response times of each of the tasks and the complications introduced by communications costs.

From the processors point of view, the schedulability analysis for single processor systems developed by Liu and Layland [5] needed to be extended to guarantee that no task will miss its deadline due to the occurrence of a fault.

In this work we integrate fault tolerance techniques into a multiprocessor hard realtime system. This multiprocessor system considered consists of a set of processors interconnected by a CAN (Controller Area Network) bus. The basic analysis tool for fault tolerant real-time systems is task scheduling; scheduling considers early action on the prediction that timing constraints may be missed. We introduce extensions to the ratemonotonic scheduling algorithm applied to the CAN bus communication protocol. A new method to solve the CAN protocol problems is also proposed, allowing its use in hard realtime applications. The incorporation of time redundancy in conjunction with hardware and software redundancy are used to enhance the fault-tolerance capability of the CAN protocol to tolerate faults in hard real-time systems.

## **1.3 Related Work**

Embedded systems exhibit stringent constraint including physical size, code size, timeliness, power and cost constraints. At the same time, if these systems fail, damage to lives and/or property can result, thereby requiring a high degree of reliability. The development of embedded systems has been one of the important research lines in the Carnegie Mellon University, where a Specification and Verification Center [24] was created and projects like

IMAGES (Integrated Modeling for Analysis and Generation of Embedded Software) [22], MoBIES (Model-Based Integration of Embedded Systems) [23] are going on.

The variety of metrics suggested for real-time systems indicates the different types of real-time systems that exist in the real world as well as the types of requirements imposed on them. Tasks can be associated with computation times, resource requirements, importance levels (sometimes also called priorities or criticalness), precedence relationships, communication requirements, and of course, timing constraints.

Several methods of priority have already been proposed for providing fault-tolerance to HRTSs on a uniprocessor or multiprocessor platform. Problems with task priority in HRTSs have already been shown as being NP-hard class problems [1], [2], and [3]. A further difficulty that occurs in the NP-hard class of problems is the scheduling of periodic tasks with arbitrary deadlines [4]. Many heuristics have been proposed to prioritize periodic tasks.

Effective scheduling involves allocating resources and time to activities in a way that allows a system to meet certain performance requirements. Scheduling is perhaps the most widely researched topic in real-time systems because many researchers believe that ensuring that tasks will meet deadlines are the key factor that distinguishes real-time systems from nonreal-time systems.

The traditionally adopted dynamic approach is priority-based preemptive scheduling. In this approach, tasks have priorities that may be statically or dynamically assigned. At any given time, the task with the highest priority is executed. Preemption is necessary if a low-priority task is being executed and a higher-priority task arrives. If priorities are assigned systematically, - using the rate-monotonic approach [5], for example, - utilization boundaries can be derived. If a set of tasks does not exceed the boundaries, they can be scheduled without missing any deadlines.

Liu and Layland [5] introduced the Rate-Monotonic Algorithm (RMA) to prioritize periodic tasks in a unique processor. RMA is an algorithm for preemptively scheduling periodic tasks that designates the highest priorities to tasks with shorter periods. It is optimum when considering independent tasks running on a single processor.

The problem of scheduling periodic tasks in multiprocessors systems is considered in [1], [4], and [7]. In [1], Dhall and Liu showed that RMA is not optimum for scheduling tasks in multiprocessor systems. None of the algorithms were shown to be optimum for scheduling periodic tasks in multiprocessor systems.

Joseph and Pandya [10] demonstrated the Completion Time Test (CTT) in order to verify the schedulability of a fixed set of periodic tasks in a processor. RMA was generalized for multiprocessor systems by Dhall and Liu [1], who proposed the heuristic Rate-Monotonic First-Fit (RMFF).

Pandya and Malek [14] showed that in a process for re-executing a task that has failed in a fault-free instance, as proposed in [11], the priorities should be maintained by RMA. Under those conditions, none of the tasks will lose its deadline, even in the presence of faults, if the processor utilization factor is not higher than 0.5.

Bertossi and Mancine [15] proposed the Fault-Tolerant Rate-Monotonic First-Fit (FTRMFF) to provide fault-tolerance to a HRTSs. They use a multi-processed system where each task has a passive or active copy in another processor, and the whole set of tasks is prioritized by RMFF, supporting fail-stop of one or more processors.

The emergent development of real-time communication protocols stimulated the research in multiprocessor hard real-time systems and fault tolerance fields, where the task schedulability needs to be guaranteed for a certain fault model specified.

Tindell and Clark presented in [9] a holistic schedulability analysis for distributed hard real-time systems, extending the current analysis associated with static priority preemptive based scheduling to address the wider problem of analyzing schedulability of a distributed hard real-time system. In their work, a simple Time Division Multiple Access (TDMA) protocol is assumed and analysis developed to bound not only the communications delays, but also the delays and overheads incurred when messages are processed by the protocol stack at the destination processor.

### **1.4 Contributions**

In this work, we use task schedulability and time redundancy to optimize faulttolerance requisites for multiprocessor hard real-time systems. The schedulability analysis for single processor systems developed by Liu and Layland [5] was extended to guarantee that no task will miss its deadline due to the occurrence of a fault. This extension, called RMCAN, provides guarantees that a CAN bus can tolerate faults. A maximum transmission rate for each message instance is defined instead of pre-defining a time-driven slot (as is the main idea of TTP/C). With this restriction, a node transmission is not limited to its slot, but it may occur at any time if its transmission rate permits. Another important contribution of this thesis is the definition of a Fault Tolerant Hard Real-Time (FTHRT) architecture consisting of processors executing in parallel exchanging data through a CAN bus. The incorporation of fault tolerance in a scenario with this characteristic includes the definition of how a scheduling approach such RMS must be applied in the tasks scheduling process and how the communication bus must be adapted to provide a guaranteed response time for the CAN bus. These enhancements introduced new possibilities for the development of systems and applications. A DSP based FTHRT architecture was implemented and a case study shows clearly the application of the concepts and ideas developed.

From the main contribution, other contributions follow:

- Definition of RMCAN, which is an extension to the CAN protocol where a recovery scheme for single or multiple faults is applied to the bus in conjunction with Rate Monotonic message scheduling.

- Application of the Fault-Tolerant Hard Real-Time architecture proposed for multiple configurations in the power electronics field.

- Application of the concepts developed and RMCAN to a real case where an Uninterruptible Power Supply is implemented to provide power to its loads.

- Make it possible to provide guarantees required for fault-tolerant execution in real-time systems.

- Formal integration of time and processor redundancies, based on the Rate Monotonic Analysis, to enhance the fault tolerance capability of multiprocessor Hard Real-Time Systems.

#### **1.4.1 Publications and other contributions**

A list o publications related to the thesis is present below:

5th IEEE Latin-American Test Workshop - RMCAN - A protocol for multiprocessor fault tolerant architectures. M. P. Oliveira, A. O. Fernandes, S. V. A. Campos, A. L. A. P. Zuquim, A. R. Beckler, Cartagena, Colombia, 2004.

- 9<sup>th</sup> ICC Guaranteeing fault tolerance through scheduling on a CAN bus. Marcos Pêgo de Oliveira, Antônio Otávio Fernandes, Sérgio Vale Aguiar Campos, Ana Luiza de Almeida Pereira Zuquim, José Monteiro da Mata. Proceedings of the 9<sup>th</sup> International Can Conference, October/2003.

- WTF2003 Guaranteeing Fault Tolerance through Scheduling on a CAN Bus. Marcos Pêgo de Oliveira, Antônio Otávio Fernandes, Sérgio Vale Aguiar Campos, Ana Luiza de Almeida Pereira Zuquim. Proceedings of the IV Tests and Fault Tolerant Workshop, May/2003.

- VIII SCTF Deadline: Um Núcleo Multi-Tarefas Tolerante a Falhas para Sistemas de Tempo Real. Marcos Oliveira, Antônio Otávio Fernandes, Claudionor J. N. Coelho Jr.. VIII Simpósio de Computação Tolerante a Falhas pp.49-53. Instituto de Computação, Universidade Estadual de Campinas 1999.

An important contribution of this work is the use of the concepts and ideas in the development of a Three-phase 80Kva UPS as a fault-tolerant multiprocessor system. The concepts and ideas presented here culminated on the development of a fault-tolerant multiprocessed UPS and complemented the work developed on several other researches:

- "Desenvolvimento de um sistema de energia ininterrupta monofásica" Leandro Oliveira. Master´s Thesis DELT/EEUFMG 2003.

- "Controle Digital de Uma Ups Trifásica" Cláudio Henrique Fortes Felix, Master's Thesis DELT/EEUFMG 2003.

- "Power Management for Communication Intensive Real-Time Embedded Systems" - Ana Luiza de Almeida Pereira Zuquim, Master's Thesis DCC/UFMG 2002.

- "Desenvolvimento de uma UPS trifásica / monofásica de 6kVA" Paulo de Tarso Paixão Lopes, Master´s Thesis DELT/UFMG 2000.

- "Agente Proxy Embutido para Gerência de Ups " Wilton de Castro Padrão, Master's Thesis DCC/UFMG 1999.

• "SupsWeb-Gerenciamento de No-breaks Baseado na Web" - Carlos Leonardo Mendes, Master's Thesis DCC/UFMG 1999.

### **1.5 Organization**

This work is organized in the following form. In Chapter 2 real-time systems and the main concepts of fault tolerance in real-time systems are introduced. The goals of fault-tolerance projects are introduced and exemplified. In Chapter 3 the main schedulability concepts of periodic and aperiodic tasks in real-time systems are introduced and discussed. In Chapter 4 real-time protocols, with fault tolerance requisites are introduced and discussed. In Chapter 5 the proposed approaches, models, perspectives and schedule algorithms are shown. The developed approach is presented in Chapter 6. In Chapter 7 we presented some conclusions and discuss the main contributions of this work.

## Chapter 2

## **Fault Tolerance in Real-Time Systems**

#### 2.1 Overview

An erroneous concept about real-time computation is that fault tolerance is orthogonal to the needs of real-time. It is frequently assumed that the characteristics of availability and of reliability of the system are independent of characteristics of time. However, this position does not take into consideration an inherent characteristic of real-time systems: that is, correct operation of the system is not dependent on only the logical correct result of the computation, but also on the deadline by which this logical result is reached. In other words, real-time systems can fail due to hardware and/or software faults, as well as by not answering, due to characteristics of the system, within the required time constraints, which is usually imposed by the environment [13].

In fact, if the correct logical result is dependent on characteristics of time, then separating the functional specifications of the time specifications can be a very difficult task. Furthermore, requisites of fault tolerance can add even greater constraints to the system. For example, frequent tests and recovery routines increase the characteristic of fault tolerance; at the same time, however, they can increase the possibility of the system missing the specified deadline.

When the specification of a system demands a certain service to be attended to by a certain deadline, the inability of the system to meet this specified constraint may be seen as a fault of the system. However, the simple approach of assuming the project method of a fault-tolerant system will treat missing a deadline as a time fault of the system; it will not attend to the needs of fault tolerance in real-time systems. The fundamental difference is that real-time systems have to be able to predict that the deadline will be missed, enabling thus the possibility of taking a certain action before such a fault occurs [13][18]. In this way, fault tolerance and real-time specifications should be considered concomitantly in all phases of these types of projects. The challenge is to include the needs of time and fault tolerance in the

specifications of the project on all abstract levels. It is essential to adopt a project methodology that considers prediction in all phases, including the time of the fault detection, isolation, reconfiguration of the system, and recovery.

#### 2.2 Real-time Systems

Typically, a real-time system consists of a controlled system and a driver system. For example, in an automated factory the controlled system is the factory floor plus their robots, mounting stations and pieces to be mounted. The controller system is the computer and the man-machine interface, which manages and coordinates the activities on the factory floor. Therefore, the factory itself can be seen as the environment with which the computer must interact.

Real-time systems are characterized by the fact that severe consequences will occur if the system's logical results and time constraints are not reached. As explained, real-time systems differ from traditional systems because of the deadline involved and because of other characteristics of time, which are linked to the tasks specific constraints. Therefore, the system is in a position of attributing an explicit commitment between performance and a correct logical result. Faults, including time faults, can cause catastrophic consequences [30]. This means that, different from systems that separate a correct result from a deadline, real-time systems strongly interlink a correct logical result and performance in accordance with a deadline. In this way, real-time systems need to solve the problem of missing the deadline, taking into consideration the specific context of the target application. The sooner that the system determines that it will miss the deadline, the sooner the system can readjust its decision-making based on the new context of the application [18].

Real-time systems are based on the premise that the worst-case execution time of the program is precisely known. The worst-case execution time of the program is dependent on the system hardware, the operating system, the compiler and the programming language used [18]. Many authors proposed different applications of the worst-case execution-time analysis for different processor architectures [83][84][85]. Many characteristics of underlying hardware that have been introduced to increase performance affect the problem of finding the worst-case execution time [31]. In this way, the omnipresence of caches as well as of pipelines, dynamic RAMs, virtual memory, etc., makes the behaviour of the hardware non-deterministic. Likewise [32], compilers with optimizers that have been implemented targetting

to obtain the best performance for a specific architecture can contribute to a poor prediction of the execution time of the generated code. These techniques, although useful in other ways, are not compatible with the goal of predicting the worst-case execution times. Examples of these optimization techniques include "constant folding", "value propagation", "redundantassignment elimination", "partial-redundancy elimination", "common sub-expression elimination", "flow optimization", "dead-code removal", "loop-invariant code motion", "strength reduction", "induction variable elimination", and "register allocation by coloring"[18][33][34]. System interference in the form of servicing interrupts, referring to shared memory and context-switching also complicates the situation. In short, any attempt to determine execution time statically in real-time programs reveals a high level of complexity.

The characteristics of time with regard to a task can be arbitrarily complex, but among the most common characteristics is the one of periodicity. A periodic task has a deadline by which it should initiate or conclude; it can also have a double characteristic at the beginning and at the terminus. This characteristic of periodicity of tasks allows one to separate verification of the correct logical operation of the computation from verification of the deadline at which this result is reached, as the next chapter explains in detail.

#### **2.3 Fault Tolerance**

There are a great number of referring concepts, which underly fault-tolerant computation. It is important to have these concepts well defined in order to fully understand the subject.